# Method and Implementation of Multi-Channel Correlation in the Hybrid CPU+FPGA System

**Maxim Leonov**

A thesis submitted to

Auckland University of Technology

in partial fulfilment of the requirements for the degree of

Master of Engineering (ME)

2009

**School of Engineering**

Primary Supervisor: Dr. Slava Kitaev

## **Abstract**

Modern high-performance digital signal processing (DSP) applications face constantly increasing performance requirements and are becoming increasingly challenging to develop and work with. In DSP paradigm, many researchers see potential in achieving algorithm speed-up by employing Field Programmable Gate Arrays (FPGAs) – reconfigurable hardware with parallelism feature. However, developing applications for FPGAs incur particular challenges on the development flow.

This work proposes a scalable hybrid DSP system for performing high-performance signal processing applications. The system employs a hybrid CPU+FPGA architecture of commercially available, off-the-shelf (COTS) FPGAs and central processing units (CPU) of personal computers.

In this work an example implementation of a multi-channel cross-correlator is investigated and delivered using a new development paradigm. The correlator is implemented on the XD1000 development system using a high-level FPGA programming tool – Impulse CoDeveloper. Analysis of DSP application development in a hybrid CPU+FPGA system employing the high-level programming tool Impulse C is presented. Potential of the selected tool to deliver algorithm speed-ups is investigated using reference multi-channel correlator software.

Particular attention is devoted to input/output (I/O) implementation, which is considered one of the most challenging problems in FPGA design development. This work delivers an I/O framework based on PCI Express interface for the proposed high-performance scalable DSP system. Using Stratix II GX PCI Express Development Board from Altera Corporation, a scalable and flexible communication approach for the multi-channel correlator is delivered. This framework can be adapted to perform other high-performance streaming DSP applications.

The outcomes of this work are a multi-channel correlator developed in a reconfigurable environment with new design methodology and I/O framework with software control application. The outcomes are used to demonstrate the potential of implementing DSP applications in a hybrid CPU+FPGA architecture and to discuss existing challenges and suggest possible solutions.

# Acknowledgements

I would like to acknowledge the support and guidance of my supervisor, Dr. Slava Kitaev, whose patient advice and encouraging directions always came at the right time and without whom I would never have completed this work. I would also like to thank Dr. Hamid Gholam Hosseini for his valuable participation during the first part of the project.

I would also like to express my gratitude to Altera Corporation for providing discounts for hardware. Separately, I would like to thank an Altera support team representative, Steven, for providing invaluable help and adviceduring my experience with Altera hardware.

A separate gratitude is due to Impulse Accelerated Technologies for generously providing extended evaluation licence for their product, which allowed me to complete this project. Impulse C support team also deserves acknowledgment, without whose participation very little, if any at all, progress would have been made.

I would also like to thank XtremeData, Inc. for supplying the hardware with academic discount.

I thank Jungo Ltd. for providing evaluation licence for their software.

An appreciation goes also to Aidan Hotan from the University of Tasmania, who helped with initial experiments of this project.

Finally, I would like to thank my parents and friends for their patience and understanding during completion of this thesis.

# **Table of Contents**

| Abstract                                               | iii         |

|--------------------------------------------------------|-------------|

| Acknowledgements                                       | iv          |

| Table of Contents                                      | v           |

| Attestation of Authorship                              | viii        |

| List of Abbreviations                                  | ix          |

| List of Tables                                         | xi          |

| List of Figures                                        | xii         |

| List of Documents on CD-ROM                            | xiv         |

| Chapter 1. Introduction                                | 1           |

| 1.1 Background                                         | 1           |

| 1.2 Research Objectives                                | 6           |

| 1.3 Thesis Layout                                      | 7           |

| Chapter 2. Theory Background and Related Work          | 9           |

| 2.1 Typical High-Performance Signal Processing Applica | ations9     |

| 2.1.1 Radio Astronomy                                  | 10          |

| 2.1.2 RADAR Applications                               | 11          |

| 2.1.3 Medical Applications                             | 13          |

| 2.1.4 Telecommunication                                | 14          |

| 2.2 Correlation as a Typical DSP Application Problem   | 15          |

| 2.2.1 Correlation Theory                               | 16          |

| 2.2.2 Digital Correlators                              | 17          |

| 2.2.3 Implementations of Correlators                   | 18          |

| 2.3 DSP Technologies                                   | 20          |

| 2.3.1 The Performance Requirements of the DSP App      | lications20 |

| 2.3.2 Digital Signal Processors (DSPs)                 | 21          |

| 2.3.3 Application-Specific Integrated Circuits (ASICs) | )22         |

| 2.3.4 High-Performance Computing                       | 24          |

| 2.3.5 FPGAs as a DSP Tool                              | 25          |

| 2.3.6 CPU+FPGA Hybrid Approach                         | 27          |

| 2.4 Chapter Summary                                    | 28          |

| Chapter 3. Hybrid CPU+FPGA Architecture                | 29          |

| 3.1 Hybrid CPU+FPGA Architecture                       | 29          |

| 3       | .1.1  | FPGA Technology                                                      | 30       |

|---------|-------|----------------------------------------------------------------------|----------|

| 3       | .1.2  | Challenges in FPGA Programming                                       | 33       |

| 3       | .1.3  | High-Level Programming for Hybrid Architectures                      | 34       |

| 3       | .1.4  | Hybrid Systems                                                       | 37       |

| 3.2     | Proj  | posed High-Performance Hybrid DSP System                             | 39       |

| 3.3     | Cha   | apter Summary                                                        | 41       |

| Chapter | 4. M  | lethodology and Design Flow                                          | 43       |

| 4.1     | Proj  | ject Design Flow and Methodology                                     | 43       |

| 4.2     | Dev   | velopment Hardware Platform                                          | 44       |

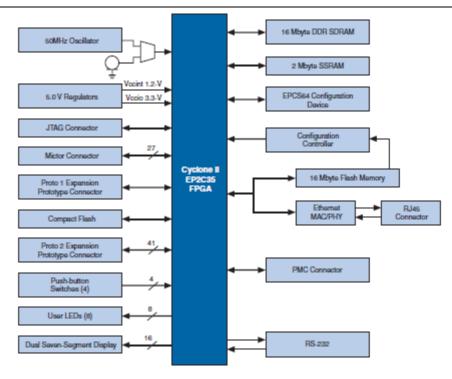

| 4       | .2.1  | Nios II Development Kit Cyclone II Edition                           | 44       |

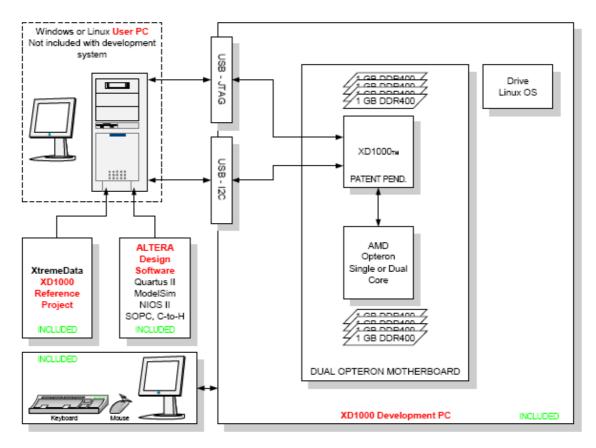

| 4       | .2.2  | XD1000 Development System                                            | 45       |

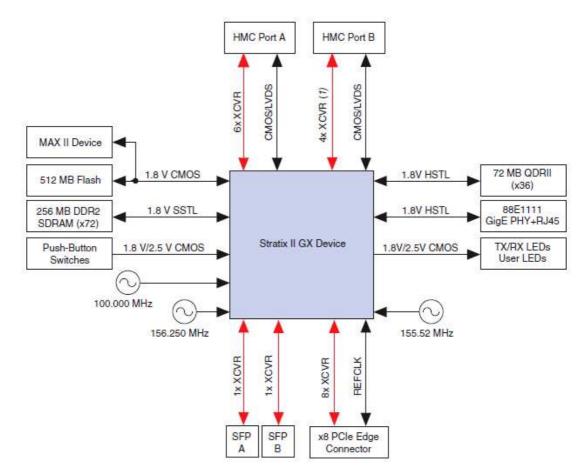

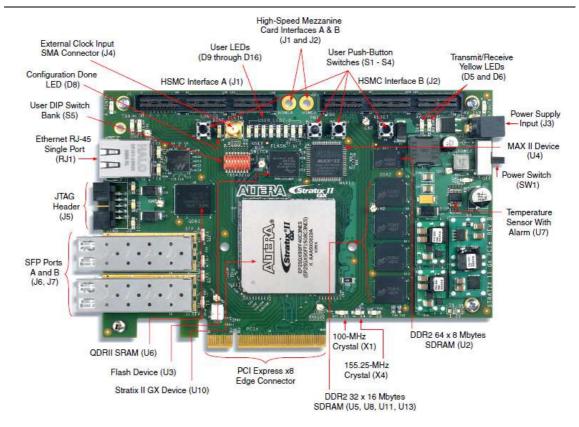

| 4       | .2.3  | PCI Express Development Kit Stratix II GX Edition                    | 46       |

| 4.3     | Dev   | elopment Software Tools                                              | 49       |

| 4       | .3.1  | FPGA Development Tools                                               | 49       |

| 4       | .3.2  | New Hardware Design Methodology                                      | 51       |

| 4       | .3.3  | Software Development Tools                                           | 58       |

| 4.4     | Cha   | npter Summary                                                        | 59       |

| Chapter | 5. In | nplementation                                                        | 60       |

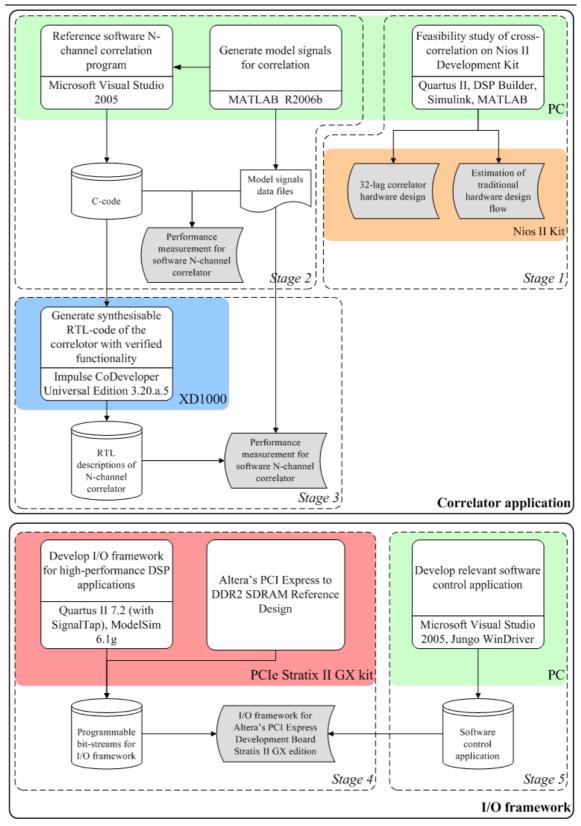

| 5.1     | Imp   | olementation Flow                                                    | 60       |

| 5.2     | Def   | ining Approaches                                                     | 62       |

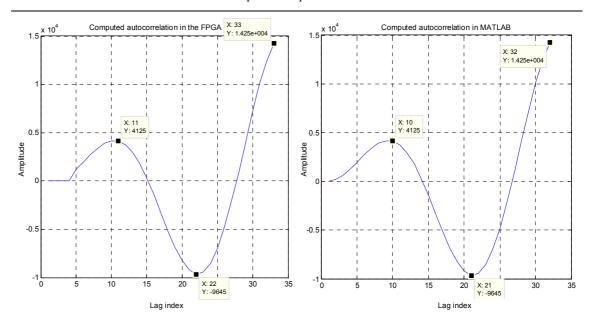

| 5       | .2.1  | Trial Hardware Correlator's Design (Stage 1)                         | 62       |

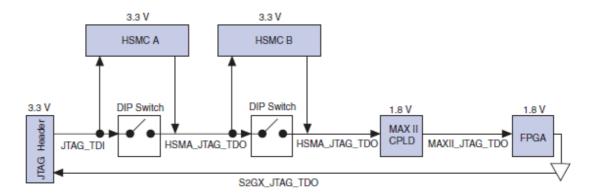

| 5       | .2.2  | Problem Positioning for Stages 2–5                                   | 64       |

| 5.3     | Imp   | plementations for Stages 2–5                                         | 66       |

| 5       | .3.1  | Reference Software N-Channel Correlation Program (Stage 2)           | 66       |

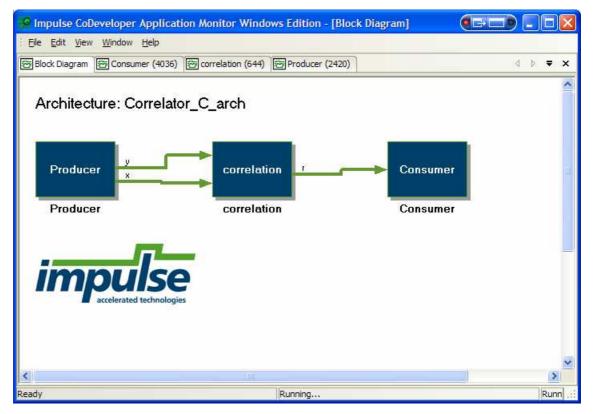

| 5       | .3.2  | Hardware Implementation of the Correlator in Impulse CoDe            | evelopei |

| (?      | Stage | 23)                                                                  | 68       |

| 5.4     | I/O   | Framework (Stages 4 and 5)                                           | 73       |

| 5       | .4.1  | PCI Express to DDR2 SDRAM Reference Design from                      | Altera   |

| C       | Corpo | ration                                                               | 73       |

| 5       | .4.2  | Developed I/O Framework (Stage 4)                                    | 75       |

| 5       | .4.3  | Software Control Application (Stage 5)                               | 77       |

| 5.5     | Cha   | pter Summary                                                         | 78       |

| Chapter | 6. R  | esults                                                               | 80       |

| 6.1     | Cor   | relator Design (Stage 3)                                             | 80       |

| 6.2     | I/O   | Framework with Software Control Application (Stages 4 and 5) $\dots$ | 84       |

#### Table of Contents

| Chapter 7. Discussion                                                  | 85    |

|------------------------------------------------------------------------|-------|

| 7.1 Discussions                                                        | 85    |

| 7.1.1 Correlator Design                                                | 85    |

| 7.1.2 I/O Framework                                                    | 89    |

| 7.2 Future Work                                                        | 90    |

| 7.3 Summary                                                            | 92    |

| References                                                             | 96    |

| Appendix A1. Components of the 32-lag Hardware Correlator Design       | 102   |

| Appendix A2. Simulink Test Model for 32-lag Hardware Correlator Design | gn105 |

| Appendix A3. MATLAB Script to Generate Model Signals for Correlation   | n 106 |

| Appendix A4. Reference Software N-Channel Correlation Program          | 107   |

| Appendix A5. 6-Channel Correlator Impulse CoDeveloper project          | 109   |

| Appendix A6. Files Modified from the Original PCI Express to DDR2 S    | DRAM  |

| Reference Design                                                       | 118   |

| Appendix A7. The Switch                                                | 142   |

| Appendix A8. The Correlator's DDR Controller Driver                    | 144   |

| Appendix A9. Software Control Application                              | 160   |

# **Attestation of Authorship**

I hereby declare that this submission is my own work and that, to the best of my knowledge and belief, it contains no material previously published or written by another person (except where explicitly defined in the acknowledgements), nor material which to a substantial extent has been submitted for the award of any other degree or diploma from a university or other institution of higher learning.

## **List of Abbreviations**

ADC Analog-to-Digital Converter

ASIC Application-specific Integrated Circuits

CDMA Code Division Multiple Access

CLB Configurable Logic Block

COTS Commercial, Off-The-Shelf

CPLD Complex Programmable Logic Device

CPU Central Processing Units

DAC Digital-to-Analog Converter

DDR Double Data Rate

DMA Direct Memory Access

DSP Digital Signal Processing or Digital Signal Processor

ESL Electronic System Level

FPGA Field Programmable Gate Array

GPP General-Purpose Processor

HDL Hardware Description Language

HLL High-Level Language

HLP High-Level Programming

HMC High-speed Mezzanine Connectors

HPC High-Performance Computing

HSMC High-Speed Mezzanine Connectors

I/O Input/Output

JTAG Joint Test Action Group

LE Logic Element

MIPS Million Instructions Per Second

MMAC Million Multiply Accumulate Operations

MPI Message Passing Interface

MRI Magnetic Resonance Imaging

PAL Programmable Array Logic

PC Personal Computer

PCI Peripheral Component Interconnect

PCIe Peripheral Component Interconnect Express

PCI-X Peripheral Component Interconnect Extended

PSP Platform Support Package

RADAR RAdio Detection And Ranging

RAM Random Access Memory

RC Reconfigurable Computing

RF Radio Frequency

RTL Register Transfer Level

SAR Synthetic Aperture Radar

SDRAM Synchronous Dynamic Random Access Memory

SFP Small Form-factor Pluggable

SOC System On Chip

USB Universal Serial Bus

UWB Ultra-Wideband

VLSI Very Large-Scale Integrated

# **List of Tables**

| Table 5.1. Correlator Parameters Summary                                    | 66        |

|-----------------------------------------------------------------------------|-----------|

| Table 5.2. Memory Address Space in PCI Express to DDR2 SDRAM Reference      | ce Design |

| (Altera Corporation, 2006)                                                  | 78        |

| Table 6.1. Number of Output Cross-Products Depending on the Number          | of Input  |

| Channels                                                                    | 81        |

| Table 6.2. Performance Results Data of Software and Hardware Implementation | ons83     |

| Table 7.1. Achieved Simulation Speed-ups                                    | 86        |

# **List of Figures**

| Figure 1.1. Performance Gap Between Traditional Processor Architectures and Gr        | rowing  |

|---------------------------------------------------------------------------------------|---------|

| Complexity of DSP Algorithms (Telikepalli & Fiset, 2006)                              | 4       |

| Figure 2.1. Generic Digital Processing Scheme (Mitra, 2006)                           | 9       |

| Figure 2.2. Basic RADAR Principle                                                     | 12      |

| Figure 2.3. The DSP Performance Gap in Communications Industry (Ganousis, 20          | 004)21  |

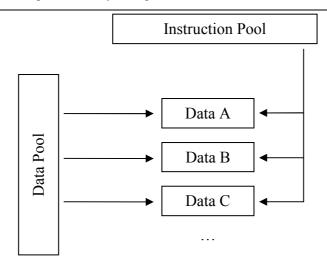

| Figure 2.4. Single Instruction, Multiple Data (SIMD) Model                            | 25      |

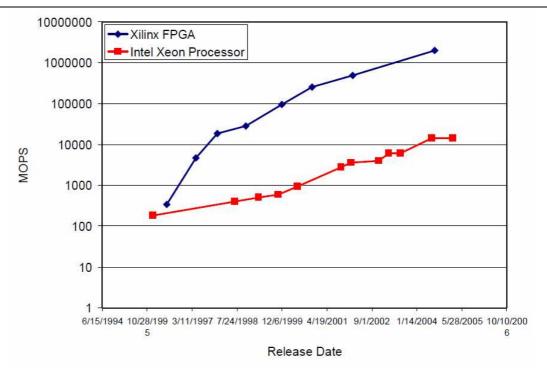

| Figure 2.5. Moore's Law in the CPU and FPGA World (Chen Chang, 2005)                  | 27      |

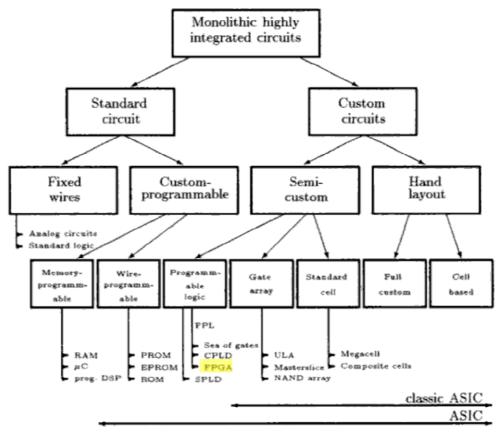

| Figure 3.1. Classification of VLSI Circuits (Meyer-Baese, 2004a)                      | 30      |

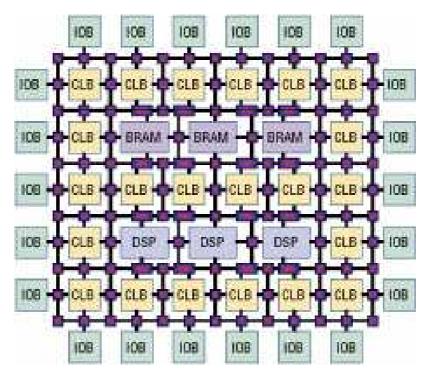

| Figure 3.2. A Generic FPGA Architecture (Gokhale & Graham, 2005)                      | 31      |

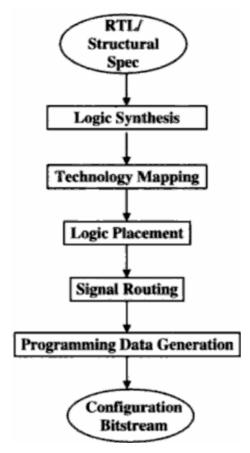

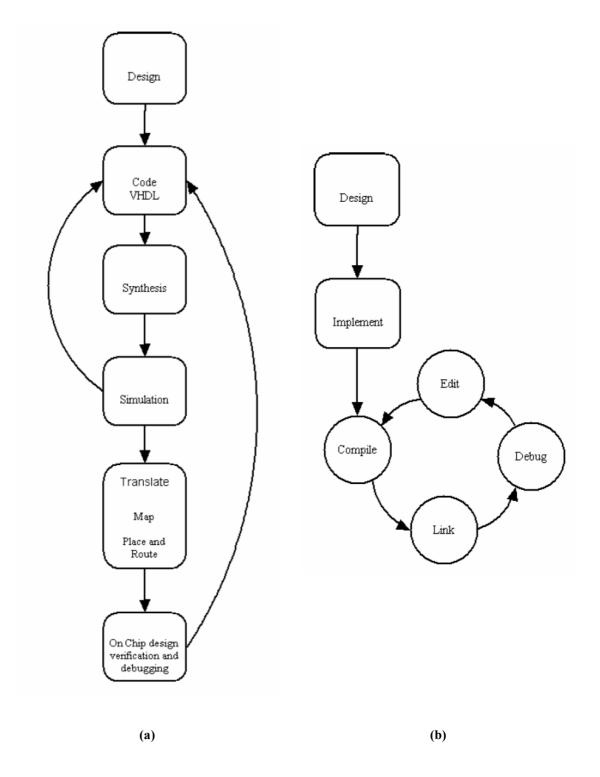

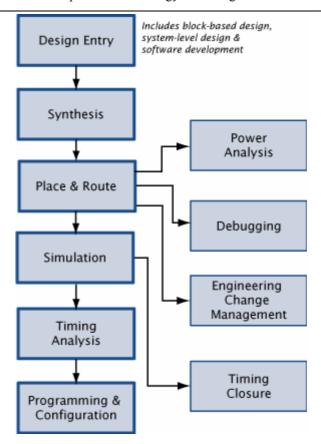

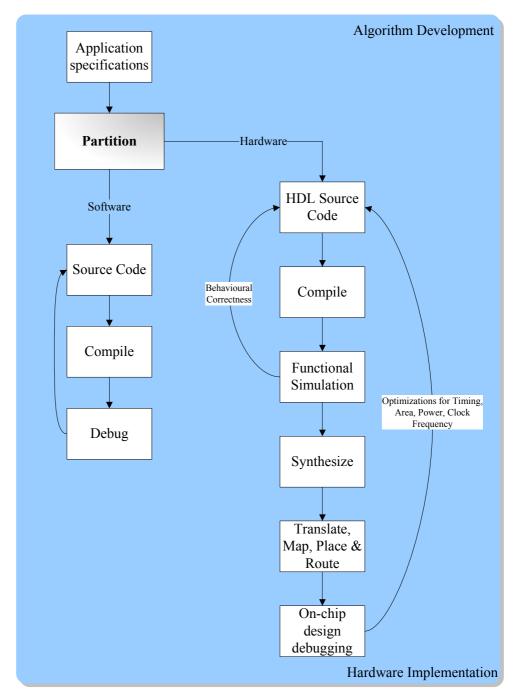

| Figure 3.3. Low-level FPGA Design Flow (Gokhale & Graham, 2005)                       | 32      |

| Figure 3.4 Hardware (a) and Software (b) Design Flows (Wain et al., 2006)             | 34      |

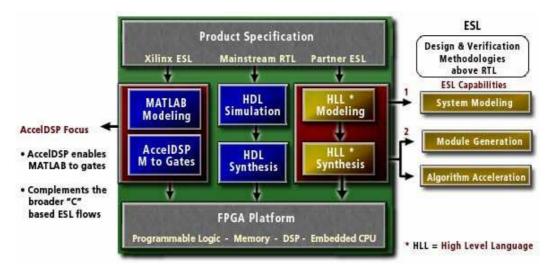

| Figure 3.5. FPGA Electronic System Level (ESL) Approach (Xilinx Inc.)                 | 35      |

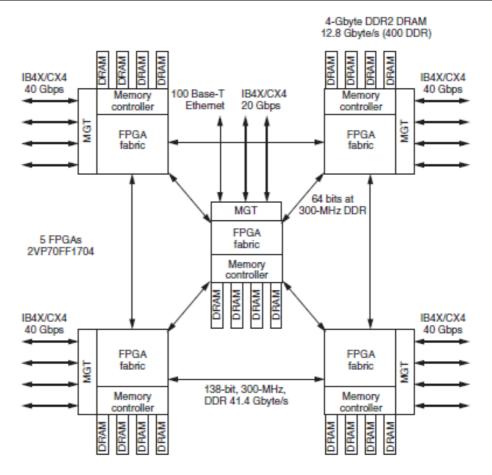

| Figure 3.6. Block Diagram of BEE2 Computer Module (C. Chang et al., 2005)             | 39      |

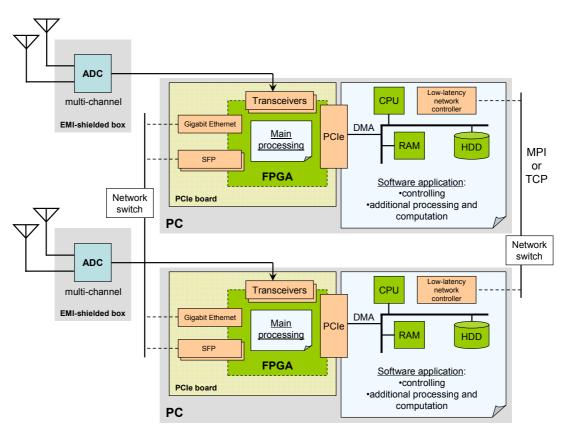

| Figure 3.7. Framework for High-Performance Hybrid DSP System                          | 40      |

| Figure 4.1. Top view of the Nios II Development Kit (Altera Corporation, 2007c)       | 45      |

| Figure 4.2. Block diagram of XD1000 Development System (XtremeData)                   | 46      |

| Figure 4.3. Stratix II GX PCI Express Development Board (Altera Corporation, 2        |         |

| Figure 4.4. Top View of the Stratix II GX PCIe Development Board (Corporation, 2007d) | (Altera |

| Figure 4.5. Design Flow in Quartus II Software (Altera Corporation, 2007e)            |         |

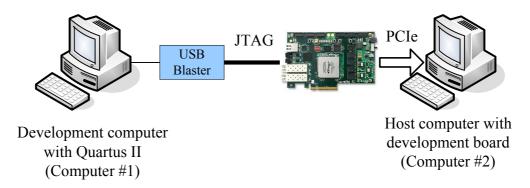

| Figure 4.6. Development Setup for PCI Express Development Kit Stratix II GX F         |         |

|                                                                                       |         |

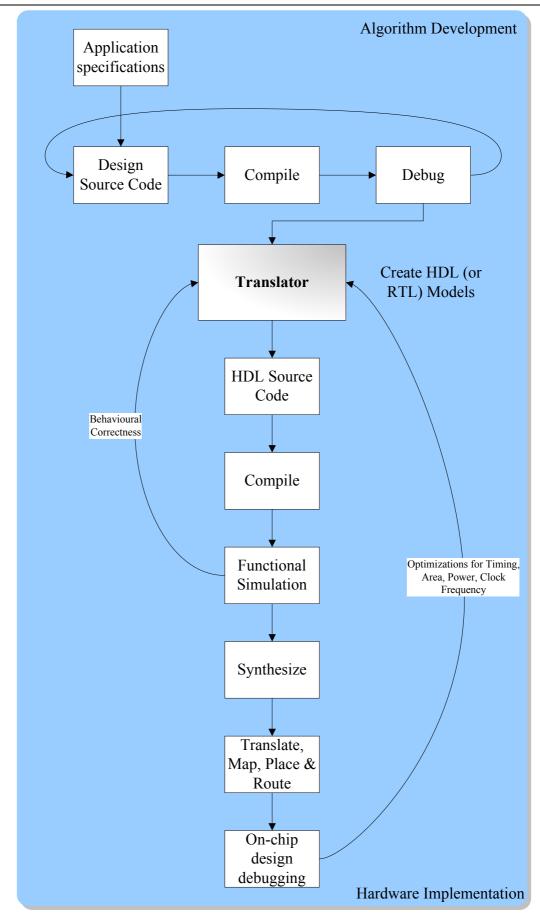

| Figure 4.7. New Top-Down Design Flow with Integrated System Level                     | 53      |

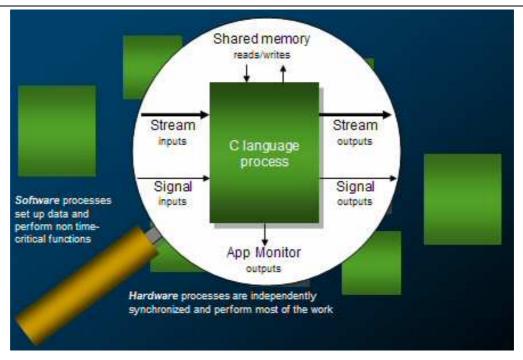

| Figure 4.8. Impulse C programming Model                                               |         |

| Figure 5.1. Implementation Flow                                                       | 61      |

| Figure 5.2. Autocorrelation Function of 5 kHz Sine Wave – Computed in the             | FPGA    |

| (left) and Computed in MATLAB (right)                                                 | 63      |

| Figure 5.3. JTAG Chain Connections in Stratix II GX PCI Express Development           | Board   |

| (Altera Corporation, 2007d)                                                           | 64      |

| Figure 5.4. Two-Channel Correlation in C                                              | 67      |

# List of Figures

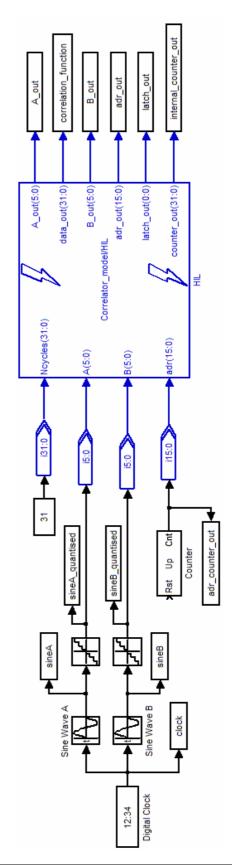

| Figure 5.5. Simulation Model of Two-Channel Correlator Running in Imp             | oulse |

|-----------------------------------------------------------------------------------|-------|

| CoDeveloper Application Monitor                                                   | 68    |

| Figure 5.6. Introducing Splitting of the Arrays in Impulse C                      | 69    |

| Figure 5.7. Using stageDelay Parameter in Impulse C                               | 70    |

| Figure 5.8. Pipeline Graph with satgeDealy values for 6-Channel Correlator Design | 71    |

| Figure 5.9. Top-Level Entity of the 6-Channel Correlator with Impleme             | nted  |

| Demultiplexors                                                                    | 72    |

| Figure 5.10. PCI Express to DDR2 SDRAM Reference Design Block Diagram (A          | ltera |

| Corporation, 2006)                                                                | 74    |

| Figure 5.11. I/O Framework Block Diagram                                          | 75    |

| Figure 5.12. Example Calls of Write and Read Functions to Onboard SDRAM Mer       | nory  |

|                                                                                   | 77    |

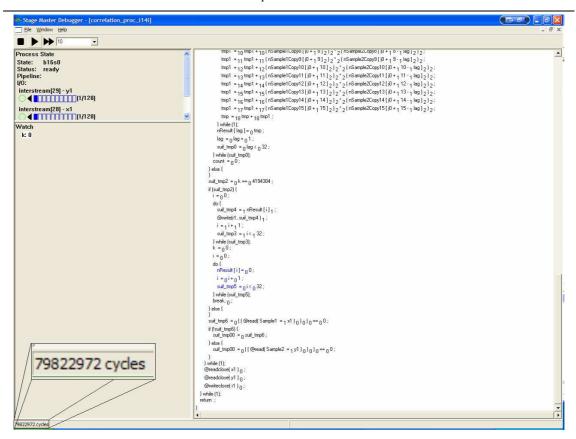

| Figure 6.1. Simulation of Hardware Implementation in Stage Master Debugger        | 82    |

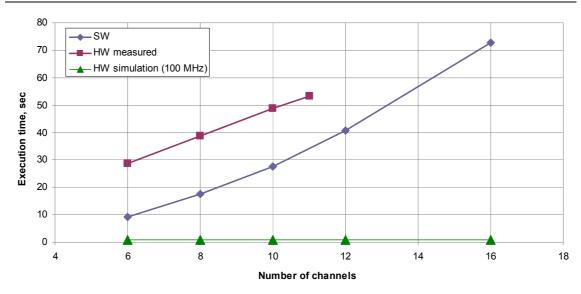

| Figure 6.2. Performance Results of Software and Hardware Implementations          | 83    |

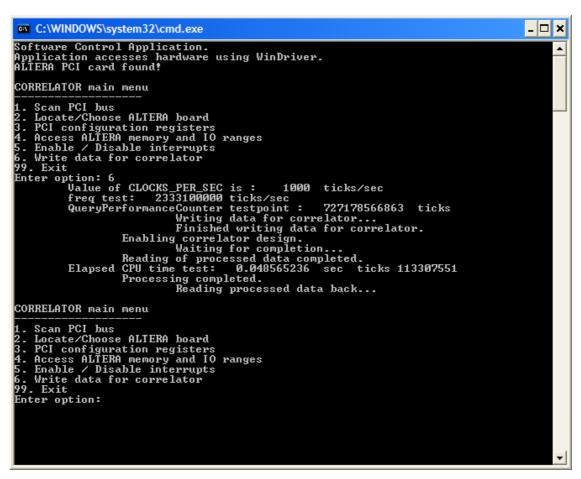

| Figure 6.3. Sample Run of Software Control Application                            | 84    |

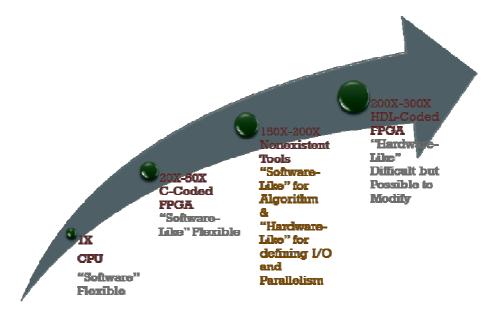

| Figure 7.1. Application Implementation Techniques (Kitaev & Molteno, 2008)        | 93    |

| Figure 7.2. Data Flow for RC System with Algorithm Partition (Gokhale & Gral      | nam,  |

| 2005)                                                                             | 94    |

## **List of Documents on CD-ROM**

#### Root folder

Thesis final (Maxim Leonov).doc – thesis file in word format

Thesis final (Maxim Leonov).pdf – thesis file in PDF format

**Folder \Impulse** C \ – correlator designs developed in Impulse CoDeveloper

**Subfolder** \6channel\_correlator\ - six-channel correlator

\6channel correlator\Correlator C hw.c – hardware source file

\6channel correlator\Correlator C sw.c – software source file

\6channel correlator\Correlator C.h - include file

\6channel\_correlator\input\_signals.txt - file with input samples

\6channel correlator\correlator out.txt – file storing correlator's output

\6channel correlator\Correlator C.exe – generated file for desktop simulation

\6channel correlator\Correlator C.icProj – Impulse C project file

**Subfolder \8channel correlator \-** eight-channel correlator

\8channel\_correlator\Correlator\_C\_hw.c - hardware source file

\8channel correlator\Correlator C sw.c – software source file

\8channel\_correlator\Correlator\_C.h - include file

\8channel\_correlator\input\_signals.txt - file with input samples

\8channel correlator\correlator out.txt – file storing correlator's output

\8channel\_correlator\Correlator\_C.exe – generated file for desktop simulation

\8channel correlator\Correlator C.icProj – Impulse C project file

**Subfolder** \10channel correlator\ - ten-channel correlator

\10channel\_correlator\Correlator\_C\_hw.c - hardware source file

```

\10channel_correlator\Correlator_C_sw.c - software source file

\10channel_correlator\Correlator_C.h - include file

\10channel_correlator\input_signals.txt - file with input samples

\10channel_correlator\correlator_out.txt - file storing correlator's output

\10channel_correlator\Correlator_C.exe - generated file for desktop simulation

\10channel_correlator\Correlator_C.icProj - Impulse C project file

```

Subfolder \11channel\_correlator\— eleven-channel correlator

\11channel\_correlator\Correlator\_C\_hw.c — hardware source file

\11channel\_correlator\Correlator\_C\_sw.c — software source file

\11channel\_correlator\Correlator\_C.h — include file

\11channel\_correlator\input\_signals.txt — file with input samples

\11channel\_correlator\correlator\_out.txt — file storing correlator's output

\11channel\_correlator\Correlator\_C.exe — generated file for desktop simulation

\11channel\_correlator\Correlator\_C.exe — Impulse C project file

Subfolder \12channel\_correlator\ - twelve-channel correlator \12channel\_correlator\Correlator\_C\_hw.c - hardware source file \12channel\_correlator\Correlator\_C\_sw.c - software source file \12channel\_correlator\Correlator\_C.h - include file \12channel\_correlator\input\_signals.txt - file with input samples \12channel\_correlator\correlator\_out.txt - file storing correlator's output \12channel\_correlator\Correlator\_C.exe - generated file for desktop simulation \12channel\_correlator\Correlator\_C.icProj - Impulse C project file

\16channel\_correlator\Correlator\_C\_sw.c - software source file

\16channel\_correlator\Correlator\_C.h - include file

\16channel\_correlator\input\_signals.txt - file with input samples

\16channel\_correlator\correlator out.txt - file storing correlator's output

\16channel correlator\Correlator C.exe – generated file for desktop simulation

\16channel correlator\Correlator C.icProj – Impulse C project file

Folder \Correlation\_reference\_program\ - correlation reference program \Correlation\_reference\_program\correlation.c - software correlation source code \Correlation\_reference\_program\input\_signals.txt - file with input samples \Correlation reference program\results.txt - file storing correlator's output

**Folder** \I\_O\_framework\ - I/O framework design with integrated six-channel correlator developed in Impulse CoDeveloper

\I\_O\_framework\hw\ – folder with exported Impulse C correlation design

\I\_O\_framework\hw\lib\tx\_ddr\_resp.v - Tx DDR2 read response state machine (from reference design)

\I\_O\_framework\rx\_pcie.v - Rx PCIe Receiver block (from reference design)

$\label{local_switch_top.v} $$ I_O_framework\switch_top.v-switch\ module $$$

\I\_O\_framework\ddr\_ctrl\_driver.v - correlator's DDR controller driver

$\label{local_state} $$ I_O_framework \cdot pcie_ddr.stp-SignalTap\ Analyzer\ file $$ I_O_framework \cdot pcie_ddr.stp-SignalTap\ Analyzer\$

\I\_O\_framework\pcie\_ddr.qpf - Quartus II project file

**Folder** \Sine\_wave\_generation\ – generation of model signals for correlation \Sine\_wave\_generation\sine\_generation.m – MATALAB script for signal generation

**Folder** \Software\_Control\_Application\ - software control operation for I/O framework

Software\_Control\_Application\altera\_diag\altera\pci\_dev\_kit\diag\altera\_diag.c - source file of software control application

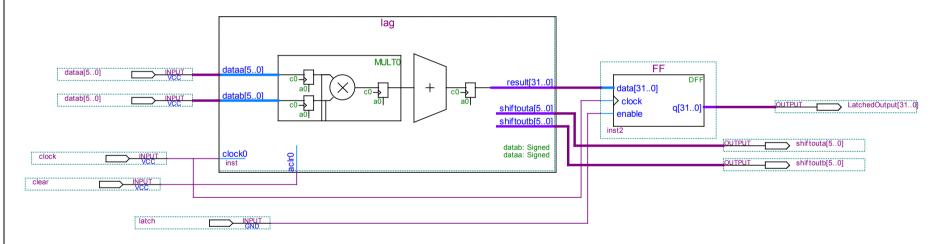

Folder \Trial\_hardware\_correlator\_design\ - trial hardware correlator design \Trial\_hardware\_correlator\_design\Correlator.vhd - VHDL top-level correlator entity \Trial\_hardware\_correlator\_design\CorrelatorLag.bdf - schematics of correlator lag \Trial\_hardware\_correlator\_design\FF.vhd - latch megafunction \Trial\_hardware\_correlator\_design\Correlator.qpf - Quartus II project file \Trial\_hardware\_correlator\_design\Correlator\_model.mdl - Simulink model \Trial\_hardware\_correlator\_design\signal.mat - MATLAB data file with input signals

# **CHAPTER 1**

#### Introduction

Necessity, who is the mother of invention.

—Plato

This chapter provides an overview of a high-performance DSP applications field from its origins to its current state. Appropriate background of the area of investigation is introduced and respective research objectives are outlined. The chapter concludes with contributions and organisations of this thesis.

### 1.1 Background

High-performance digital signal processing is very challenging work in today's engineering fields. Many applications face increasing performance demands and constant additional functional requirements. With digital signal processing becoming an integral part of everyday life, the demand for high-performance processing means has expanded rapidly in recent years.

Originally, signals in devices were manipulated using analog techniques (continuous-time domain). However, nowadays most of them are implemented in digital form (discrete-time domain). The genesis of the digital signal processing techniques can be connected to the advances in mathematical fields: finite difference methods, numerical integration method and numerical interpolation methods dating back to the seventeenth century. Of course, one of the major developments of the DSP area started in the 1950s, as a part of the far broader and embryonic field of digital computers. From the late 1960s, digital signal processing moulded into a separate field by itself. Thus, in the late 1970s when LSI (large-scale integration) technology became developed enough the realisation of a single chip DSP became practical (Mlynek, 1999). In 1978 AMI announced a "Signal Processing Peripheral" and released S2811 (Nicholson, Blasco, & Reddy, 1978) – a co-processor for a host micro. It was followed by Intel's 2920 in 1979 (Hoff & Townsend, 1979). The unique feature of the latter device was the on-chip analog-to-digital and digital-to-analog converters (ADC and DAC respectively), though

it lacked a multiplier. The DSP industry continued to grow and progress and, in the early 1980s, the world saw a second generation of DSPs with realised features like concurrency, multiple buses and on-chip memory. These were added with on-chip floating point operations in the third generation of DSPs in the early 1990s. In the late 1990s multi-processing features, image and video processors and low-power DSPs were introduced.

Contemporary signal processors are able to demonstrate much greater performance in many aspects: wider data buses and throughputs, higher processing speeds of up to 24,000 of 16-bit million multiply accumulate operations (MMACs) (Texas Instruments Inc., 2008), compatibility with various modern interfaces and buses such as PCI, USB, Ethernet and many others.

The means of performing signal processing are not, of course, limited to digital signal processors – the ever-growing field of signal processing invoked multiple solutions, architectures, technologies, tools and approaches: the major of which will be covered in the subsequent chapters of this work.

Many large-scale, high-performance DSP applications in such fields as radio astronomy, telecommunication, high-energy physics, and others involve computationally-intensive and therefore often time-consuming correlation of wideband signals. Correlation relies on the two most common types of composed DSP operations - multiply and accumulate (MAC), and multiply and add (MULT-ADD) operations. These operations have been implemented in digital processing successfully and efficiently. However, the challenge lies in the *number* of these operations, i.e. the problem size – the running time and/or space requirements of an algorithm. Many DSP applications employing correlation operation in their algorithms require real-time or near real-time processing, eg antenna aperture synthesis, medical applications, cellular and telecommunications applications (see 2.1 for details on these applications). Along with necessity to perform computations "on-the-fly", correlation involves considerable execution time or time complexity for wideband correlation. For example, a multichannel antenna array operating with 128 MHz bandwidth on each channel will yield a sampling rate of 256 MS/s with 8-bit sampling. For 8-channel correlation, this will produce 2 GB/s input data stream. Such correlation will generate 28 unique cross product outputs (the other 28 are just a mirror reflection of the first 28 (see 2.2.1)). An estimated number of operations required to perform a 32-lag correlation with these parameters is about 230 Giga-operations of real-time processing (Thompson, Moran, & Swenson, 2001a). Being a classical DSP problem, correlation itself does not usually constitute a stand-alone, full and final application, rather it is an integral part of many DSP applications.

Here and throughout this thesis channel and antenna are used interchangeably. While such notation is acceptable and coomon for engineering and DSP fields, it differs in radio-astronmy where a channel is understood as a quantum of radio frequency bandwidth.

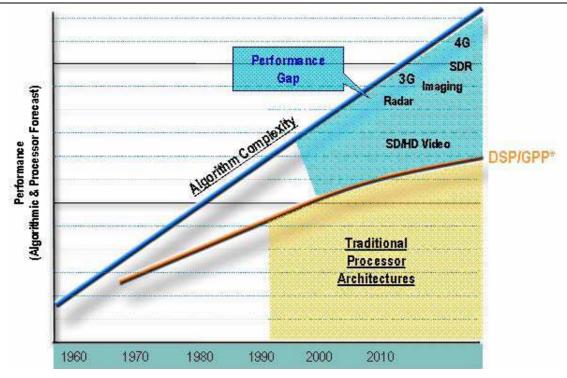

Although the processing capacity of DSP tools grew along with the requirements of the signal processing, the latter always outstands the former by considerable and everlasting margins. Almost as soon as the gap between ever-growing applications' requirements and capabilities of the DSP tools started shaping up (in the mid 1980s – see Figure 1.1) the search for counter-measures to close this gap started. The most prevalent and widely-used approach is *extensive* approach – gradual and proactive increase of the processing power of the DSP tools by increasing the number of employed computational units and/or operational parameters (operating frequencies, response times, storage capacities, etc.). Such approach proved to be productively working for Central Processing Units (or commonly known as processors), Digital Signal Processors (DSPs) and other conventional processing means for several decades and then started depleting quickly. The cost of the extensive approach hit the inevitable limitations very soon: high power consumption, complexity of dealing with growing number of computational units maintenance cost, etc.

Figure 1.1. Performance Gap Between Traditional Processor Architectures and Growing Complexity of DSP Algorithms (Telikepalli & Fiset, 2006)

No surprise, that the research vector began deviating towards technologies and methods which could offer *intensive* ways of dealing with the problem as opposed to almost exhausted extensive approaches.

Currently an intensive approach is envisioned by many researchers in *parallelism* – simultaneous execution of several computational operations during one clock cycle. Moreover, parallelisation of applications is especially effective in the DSP field as long as many DSP algorithms possess intrinsic parallelism and therefore potentially sustain a large capacity for acceleration.

Application-Specific Integrated Circuits (ASICs) possess parallelism features and reach prominent efficiency of silicon utilisation for a specific operation determined during the manufacturing stage. Thus, they can be configured to meet the requirements of the particular application avoiding unnecessary generality. Reasonably, the performance efficiency achieved by ASICs for the targeted application is balanced by the impossibility of future modifications. Many ASICS' applications do not require any updates, modifications or alterations at all (eg integrated circuits of cell phones).

ASICS' counterparts – Field Programmable Gate Arrays also possess parallelism features. Along with this, FPGAs are *reconfigurable* devices, i.e. they can be reprogrammed in the field. Adding a bug fix, a new feature or even updating a

computational core of the application, significantly increases the flexibility of design. Due to this FPGAs have lower non-recurring engineering costs than ASICS. An FPGA is a semiconductor device consisting of programmable logic blocks and programmable interconnects. Along with parallelism, reconfigurability significantly expands the application scope of these devices. Armed with these two features over the years, FPGAs became one of the most promising technologies in digital electronics in general and in the DSP field in particular.

The interest towards FPGAs has risen even more radically in recent years with the growth of the chip capacities and the number of supported interfaces, which include, but are not limited to: PCI family interfaces, Ethernet family interfaces, support for memory interfaces like DDR/DDR2/DDR3/QDRII, USB, HyperTransport, RapidIO, VMEbus and many others. Moreover, FPGAs are particularly suitable for DSP applications due to: inherited parallelism in many DSP algorithms; high bandwidths to on-chip and external memories, which support multiple access ports thus allowing further exploitation of algorithm's parallelism; streaming to-be-processed data directly to computational core implemented in FPGAs via available high-speed interfaces. Hence, these FPGAs' features make them a very attractive option for applications' acceleration or even a competitive alternative for traditional DSP techniques, attracting more and more attention from the DSP industry.

With widespread availability of commercially available FPGAs in the late 1980s, the term reconfigurable computing (RC) was introduced. A reconfigurable computing system is a system which is built from reconfigurable computing devices, eg FPGAs or FPGA-like devices. These systems have to be reprogrammable, permit orders of magnitude speed-ups versus traditional computational systems and support hardware-like levels of performance (Guccione, 2008).

However, developing DSP applications for RC systems contain many more challenges and complexities than implementing applications in traditional software programming domain of DSPs, CPUs, etc. One of the main reasons is that FPGA design flow adheres to hardware development flow, which traditionally deals with low-level hardware description languages and demands explicit configuration of available resources in FPGA. The following issues also impose substantial challenges when employing reconfigurable hardware in traditional DSP applications: hardware state ambiguity complicates design debugging; parallelism consideration and a "run-at-a-clock" concept impose certain idiosyncrasies on algorithm implementation; explicit

memory structure puts constraints on storing of design variables. Moreover, conventional processing methods (DSPs, CPU and related) have been employed in the signal processing field considerably longer than FPGAs and therefore have more advanced and powerful developing and debugging tools.

Therefore, employing FPGAs either as a computational accelerator or as a standalone DSP application platform can be beneficial and challenging at the same time. Nowadays the traditional approach of increasing the processing capacity of computational means diverge from the traditional approach of raising the number of employed semiconductors (Moore's law) and operating frequency to a multicore and parallel execution approach. Many DSP algorithms possess intrinsic parallelism. FPGAs are a very attractive and potentially beneficial option to be employed in DSP paradigms for processing acceleration. Compelling reported speed-ups of 10X to 100X (Gokhale & Graham, 2005) of equivalent software algorithms attract more and more attention from the DSP community. Another argument to employ FPGAs for DSP algorithms is that these devices follow the International Technology Roadmap for Semiconductors (ITRS) (http://www.itrs.net/) even more narrowly than modern microprocessors (eg in terms of contained SRAM memory or leading on the first fabrication lines). Many researchers agree on a high potential of simultaneous operation of conventional processing unit(s) such as a CPU of a PC and reconfigurable hardware such as FPGA (Andrews et al., 2004; Milrod, 2006; Tahernia, 2005). This architecture invokes previously unavailable possibilities and options in signal processing but it also brings new challenges in development flow.

In this thesis a new design methodology for developing applications in a hybrid CPU+FPGA environment is applied. Using a mixture of traditional hardware development tools and conventional software development tools, a multi-channel wideband cross-correlation for DSP application on a hybrid CPU+FPGA architecture will be implemented. The prime objective of this thesis is to investigate the capabilities and challenges of this reconfigurable, hybrid architecture in the DSP field.

## 1.2 Research Objectives

In this work, we will investigate the implementation of a classical DSP problem – wideband multi-channel cross-correlation in a hybrid environment of a commercial, off-the-shelf CPU and FPGA. There are a number of contributions contained within this thesis.

First, the given work addresses the problem of computational deficiency in DSP field. By implementing a classical DSP problem in a hybrid CPU+FPGA architecture, its abilities of achieving speed-ups for applications from DSP fields are argued.

The second contribution is the platform and the workflow for developing high-performance DSP applications in a hybrid CPU+FPGA environment. The development workflow applied in this work is different from a traditional hardware design methodology. Rather than using low-level HDLs for hardware design implementation, the given work utilises high-level languages (HLLs) for hardware configuration. The potential of using HLLs for FPGA designs is evaluated and discussed. The given work delivers valuable outcomes for any DSP engineer developing applications in reconfigurable hardware with the aid of high-level programming (HLP) languages.

The third contribution is that this work tackles one of the most crucial issues of DSP applications, which becomes especially challenging and difficult in the FPGA domain – input/output interfaces. The I/O framework developed in this work features original method of interfacing to FPGA via onboard SDRAM simultaneously with high-speed communication with PC via PCIe interfaces. The developed method can be beneficial to many applications requiring extensive data exchange. Particularly, it can be useful for applications targeting Altera's PCIe Development Kit Stratix II GX Edition or to any Altera's devices featuring PCIe and DDR/DDR2 SDRAM interfaces.

The given work also introduces the possible evolution of the proposed platform. The number of available interfaces on the exploited FPGA board (PCIe, Ethernet, SFP, HSMC, etc) and simple connectivity options of the conventional PC box provide a considerable degree of architectural possibilities. A highly scalable platform for high-performance signal processing is proposed as a potential future development of the created design (section 3.2). In addition, one of the advantages of the suggested platform is the affordable cost as compared to proprietary DSP solutions: the cost of the prospective system is composed merely from FPGA board's and PC box prices.

# 1.3 Thesis Layout

The thesis is organised into seven chapters. Chapter 2 briefly introduces the background of the investigated problem. Computationally intensive DSP applications employing cross-correlation of signals are discussed. Cross-correlation theory is discussed, which is followed by a discussion on DSP implementation technologies.

In Chapter 3 the notion of a hybrid CPU+FPGA architecture is introduced. Challenges existing in this architecture and high-level programming of reconfigurable hardware are discussed. The chapter also proposes high-performance DSP hybrid architecture.

Chapter 4 discusses methodology applied in this work and introduces five stages of the full project design flow. These stages define the hardware and software development tools used at every particular stage.

Chapter 5 presents implementation flow of the project. Implementation details of the stages are defined in the previous chapter.

Results and outcomes of project implementations are presented in Chapter 6. They are discussed in Chapter 7. Approaches and solutions to alleviate known shortcomings and challenges of the developed project outputs, along with future developments are suggested.

# **CHAPTER 2**

# Theory Background and Related Work

We live in a moment of history where change is so speeded up that we begin to see the present only when it is already disappearing.

—R. D. Laing

This chapter will discuss the most common digital signal processing applications in a high-performance domain. First, a brief outline of generic digital signal processing algorithm will be given. Then, the next section will highlight the most common high-performance DSP applications, which will be followed by the discussion on the cross-correlation problem as integral and often one of the most computationally intensive parts of these applications. The remaining section will present and consider contemporary DSP implementation technologies.

The term digital signal processing implies converting an analog signal into a form of numbers (digital form), the processing of the resultant sequences to either obtain information or to synthesise signals with desirable properties and possibly convert the output into analog form again. The overall scheme of the generic DSP algorithm is shown in Figure 2.1:

Figure 2.1. Generic Digital Processing Scheme (Mitra, 2006)

The high-performance DSP applications feature a considerable amount of computations in the "Digital processor" stage. Several typical high-performance DSP applications are considered in the following section.

# 2.1 Typical High-Performance Signal Processing Applications

The number of signal processing applications in today's life is truly enormous. Nevertheless, not every DSP application is suitable for reconfigurable computing. A number of studies exist which investigate efficiency criteria of an application to be

employed in FPGAs. The application's performance implemented in FPGA depends on (Hutchings & Nelson, 2008):

- 1. Data parallelism available in the application's algorithm;

- 2. Data element size and arithmetic complexity;

- 3. Amenability to pipelining, and simple control requirements.

The following sections highlight several high-performance DSP applications, which have one common and integral operation – cross-correlation of signals. The potential of implementing these applications in or with the help of reconfigurable hardware will be considered. The applications below will be considered in retrospect.

#### 2.1.1 Radio Astronomy

Throughout human history, man has been always mysteriously attracted to the sky. With the discovery and subsequent invasion of new technologies, traditional methods of visual investigation of the sky, ie methods of optical astronomy, were joined by *radio astronomy* techniques. Many astronomical bodies emit radio waves, which after certain processing can tell valuable and previously inaccessible information about their origin. Thus, in the last half of the 20<sup>th</sup> century the prominent advances in radio astronomy led to a number of foremost discoveries like masers, pulsars, radio galaxies, the Cosmic Microwave Background Radiation, etc.

With radio astronomy, scientists can study astronomical phenomena which are invisible to the human eye. While in optical observation the useful information is extracted from the spatial distribution of light across an object, ie image, radio astronomy uses a different principle. RF waves emitted by a certain phenomenon can be received and directly sampled in a time domain, thus the tools used for detecting and measuring this interaction are considerably different from optical telescopes (Carroll & Ostlie, 2007).

To produce a radio image of a celestial phenomenon a principle of *interferometry* is used, which entails the superposition technique - interference (adding or overlaying) of signals from two or more antennas. This technique is also known as *antenna aperture synthesis* when multiple antennas are used to work as one using interferometry principle.

The core idea of antenna aperture synthesis is again to superimpose the signal waves from a number of radio telescopes and, while doing so, inphase waves will add

up, while antiphase waves will cancel each other out. This creates a combined telescope with the size of the furthest observing telescopes apart. The image quality produced by such a composed antenna depends on the number of the projected separations between any two telescopes as seen from the radio source (number of *baselines*). With each radio telescope producing a data stream the processing and computational task can be extremely intensive. Besides, the processing is complicated by low signal-to-noise ratios which are common for radio astronomical observations.

The backbone operation of antenna aperture synthesis is correlation or finding the amount of similarity in the signal between two given antennas in an antenna array. The term correlation and underlying theory will be discussed more deeply in 2.2.1. Even for a medium-size antenna array, computation of correlation between all the elements of the array can be a very challenging task due to the number of involved mathematical calculations. The example considered in 1.1 with an 8-element antenna array requires  $230 \times 10^9$  operations per second. An experienced reader will estimate that the problem size of the given example as average to below average. Nevertheless, such a system might require a performance power of not less than ~230 GFlops (depending on implementation). In real-life, large-scale systems that correlate signal pairs of multi-element arrays may contain millions of correlator circuits in order to accommodate all the required antennas and spectral channels. Hence, with an increase of any of the above parameters the computational complexity of aperture synthesis grows drastically. That is why antenna aperture synthesis and radio astronomy have been established as one of the most major and demanding consumers of DSP technologies.

#### 2.1.2 RADAR Applications

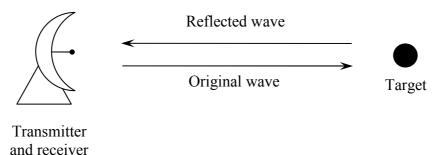

RADAR or Synthetic Aperture Radar (SAR) applications are based on the principle of the scattering of electromagnetic waves. Originally, RADAR meant RAdio Detection And Ranging, however later the term became used as a standard word. The most common RADAR system consists of a transmitter and a receiver – EM waves radiated by the transmitter are reflected (scattered) by a target, which are then collected by the receiver for further analysis. Any change in the dielectric constants of the target and a media surrounding it will be conveyed in the scattered waves. The basic principle of RADAR theory is illustrated in Figure 2.2.

Figure 2.2. Basic RADAR Principle

The gathered data can include the object's position, movement or its particular features and attributes. The range of the applications, where RADAR technique is used, is wide: weather prediction, air traffic control, threat detection systems, military missile guidance and reconnaissance radars, etc.

Antenna aperture technique as mentioned in 2.1.1 is also used in phased array radars. In such arrays, comprised of a number of similar properly displaced antenna elements, the scanning beam is controlled by operating a phase of the signal of each individual transmitting antenna. Thus, the overall transmitted signal is maximised in a desired direction and suppressed in undesired directions.

In modern RADAR applications DSP techniques are used extensively: generation and forming of the transmission pulses, controlling the antenna beam's pattern and direction, filtering of clutter, and beamforming (S.Bhaktavatsala, 2002). Cross-correlation is one of the central operations in RADAR applications: it is used to find the relation or similarity between the original and reflected waves. When applied on a largescale for multiple signals and performed in a real-time fashion, such correlation becomes a challenging task.

Substantial utilisation of RADAR techniques in military area lays particular requirements on the DSP technologies in RADAR applications, eg a common trend is the need for smaller energy-efficient systems with high processing capabilities. Furthermore, typical operational signals in RADAR are very weak and with the recent tendency of radars being operated in a dense urban environment, the task of processing such signals becomes a major challenge. This issue can be mitigated by "overlaying data from multiple sensors and known terrain features". In addition, newly-emerging digital beam-forming technologies based on a high-speed digital systems work with an ever-increasing number of scanning beams. The latter two issues increase RADAR system processing requirements considerably (Kenny, 2007).

#### 2.1.3 Medical Applications

Nonetheless, signal-processing technologies are not solely used for cognitive purposes. Perceptive, non-intrusive analytical capabilities of radio imaging make it an excellent option for diagnoses in *medical areas*. In the context of digital signal processing, the most interesting category amongst all the categories comprising the medical imaging is the ultra-wideband (UWB) imaging, which in turn is used primarily for early-stage breast cancer detection.

One of the most crucial factors in successful breast-cancer treating is detecting it at the earliest stage possible. Contemporary diagnosis methods like X-ray imaging, Magnetic Resonance Imaging (MRI), and ultrasound are capable of reducing malignant tissue. However, problems with a relatively high rate of false-negative diagnosis (Huynh, Jarolimek, & Daye, 1998) along with many unnecessary biopsies due to the low positive predictive rate (Elmore et al., 1998) make the use of X-ray mammography difficult and ineffective. Other methods like MRI and ultrasound are somewhat more effective in cancer lesions detection, yet do not always provide the necessary level of sensitivity, can be too operator specific and are very expensive.

Many of the existing drawbacks in early-stage breast-cancer detection can be alleviated with ultra-wideband imaging technology. The UWB imaging method employs the radar technique which was described in 2.1.2. A transmitting antenna (or a set of antennas) radiates a scanning burst of microwave energy. This electromagnetic energy penetrates through the target under investigation, scatters on the target, and further is collected by a receiving antenna or with an array of antennas. Then, the processing takes place with the primary goal to identify the presence and location of the considerable backscattered energy – an indication of the dielectric difference between malignant and healthy tissue. Thus, the post-processing of the received signals has to be very sensitive to filter out the necessary information from the antennas' noise, clutter due to heterogeneity in the breast tissue etc. Moreover, it has to be precise – image resolution on the order of millimetres is desirable (Li, Bond, Veen, & Hagness, 2005). Similar to RADAR applications, during the post-processing stage correlation is applied to find similarities or discrepancies in tissue readings provided by transmitted and reflected waves. Therefore, modern approaches of the existing radar application have to be adapted and improved, according to the requirements of UWB medical imaging. Now the medical diagnosis tools are still expect the DSP instruments to deliver an efficient and reliable method of breast-cancer testing.

#### 2.1.4 Telecommunication

Communication technologies are one of the most actively developing areas today. The emergence of new wireless services along with the high growth of data rates in existing services, indicates an ever-growing demand for telecommunication capacity. With worldwide deployment of 3G networks, releasing beyond-3G and 4G standards and specifications, the challenges for the DSP area keep accumulating: high data throughputs (up to 1 Gbps), multimedia communications, seamless global roaming, maintaining high user capacity, and supporting migration and the compatibility between existing previous-generation and upcoming next-generation networks, etc (Ibnkahla, 2004). Consequently, the research community is focusing on different advanced signal processing issues to achieve substantial improvements in communication systems.

To demonstrate the computation requirements that lay in the telecommunication area, an example of Code Division Multiple Access (CDMA) standards can be used. CDMA based standards (CDMA2000, W-CDMA, etc.) have become increasingly popular during the emergence of the third generation networks due to their objective to maintain the ever-growing data throughputs and efficient spectrum utilisation. In brief, the idea of CDMA implies that a number of users share the same bandwidth of frequencies and are distinguished by the individual code (pseudorandom code). Such an approach has a much higher data bandwidth than traditional Time and Frequency Division Multiple Accesses (TDMA and FDMA respectively). However, these benefits are balanced with certain difficulties. For instance, the choice and assignment of a pseudorandom code to user is not a very simple routine in highly populated large-scale mobile networks. This problem can be computationally-intensive so certain solutions were proposed to address this issue (B.-J. Chang, 2007). Similarly, an analogous problem arises on the receiving side – to decode signal from multiple users in the most efficient and fastest way. It has been indicated that this problem also has significant computational needs (Agarwal, B.V.R.Reddy, & K.K.Aggarwal, 2006).

Furthermore, the underlying complexity of the CDMA algorithm implies a challenging and complicated processing mission itself: as long as in CDMA the users share the same bandwidth the *multiple access interference* (MAI) has to be considered and alleviated. Prevention of this interference is exacerbated by the *intersymbol interference* (ISI) and multipath signal propagation which is natural to all urban mobile networks. For this purpose sophisticated *channel estimation* algorithms are applied. The computational complexity of such algorithms is considerable and furthermore they have

to be implemented in real-time fashion. Therefore, the research community has turned to elaborate DSP techniques like real-time DSPs and FPGAs to respond to these challenges (Ouameur & Massicotte, 2007).

Tackling the processing difficulties is not of course the feature of only the CDMA standard. As it was mentioned above, with the rapidly-growing rates, throughputs, capacities, etc. the industry is facing expanding requirements throughout its applications. One example is 3G and 4G mobile standards. These standards offer high data throughputs to the end-users – even comparable to office LANs' in 4G networks. To supply such high speeds, a number of advanced and complex techniques are employed in these standards. One such technique is smart antennas. To maintain high data rates in complex urban environments these antennas use adaptive beamforming and direction-of-arrival (DOA) estimation algorithms. In turn, these algorithms employ cross-correlation operation for estimation which signals arriving from which directions to suppress and which to maximise. Such calculations have to be performed with complex numbers and most importantly should be done in real-time. Thus, it is evidently seen that the necessity for high-performance signal-processing utilities spans across the whole communication industry, leaving researchers in unrelenting pursuit for an adequate response.

# 2.2 Correlation as a Typical DSP Application Problem

In many of the aforementioned applications an integral and common part can be singled out – all of them are dealing with combined sources of information providing a synergistic combination of knowledge about the investigated object. In other words, whenever a system is dealing with a number of input data streams collaboratively reducing the entropy of a studied phenomenon, the term "multi-sensor data fusion" is applied (Stergiopoulos, 2000). The integral part of this fusion is to express the joint result of analysis of two or more originally different sources. For that reason a *correlation* operation is applied, which in turn is regarded no less as a "backbone" of the whole DSP area.

Thus, the prevailing number of high-end DSP applications such as antenna aperture synthesis, radioimaging, RADAR, radio astronomy, high-energy physics and many others, has a common *and* very computationally-intensive part – the multichannel wideband correlation of signals. Correlation or, more generally speaking, finding a relation between a set of signals, is a computational core for the majority of

signal processing operations and is considerably critical for computation performance. The result of the cross-correlation function is "a measure of similarity between a pair of energy signals" (Mitra, 2006).

As it was noted before in 2.1.1, one of the applications where correlation is applied is *radio astronomy*. For example, it is used in the radio-astronomical technique known as Very Long Baseline Interferometry (VLBI). In turn, the antenna aperture synthesis is used in VLBI. The latter technique implies that the correlated product of signals from two radiotelescopes gives *visibility frequencies* of celestial object. The frequency information is obtained by averaging additional multiplications by a lagged signal and finally the data is transferred to the frequency domain by applying Fourier transform (Thompson, Moran, & Swenson, 2001b).

#### 2.2.1 Correlation Theory

A measure of similarity between a pair of signals, x[k] and y[k], is given by the *cross-correlation*  $r_{xy}[k]$  sequence:

$$r_{xy}[n] = \sum_{k} x[k]y[k-n]$$

(2.1)

where the lag index  $n \in [-N/2, N/2-1]$ , k is the time index, N is a number of lags and typically is a power of two. The lag term denotes the time-shift between the pair of signals with negative (n < 0) and positive  $(n \ge 0)$  lags being distinguished. Basically, the number of lags defines how many points or output values the correlation produces. In real life applications, where for example the correlation function is used together with Fourier transform, the number of lags can be referred as the *resolution* of correlation. A device which performs correlation of a set of signals is called a *correlator*. The number of lags is an important characteristic of a correlator along with the *number of channels*, ie number of supported input signals. When a signal is correlated with itself, such an operation is called *autocorrelation* and is often used in filtering and other processes.

One should note the incurred execution time or *time complexity* for wideband correlation. For a wideband signal according to the Nyquist condition, the processing involves computation of a greater amount of samples, hence the processing duration increases. In addition, the results of correlation computation abide to the following law (Thompson et al., 2001b):

$$N = \frac{N_S(N_S - 1)}{2}$$

(2.2)

where N is the total number of the cross-products and  $N_S$  is the total number of antennas (sources) to be correlated. Hence, wideband multi-channel correlation embraces a considerable amount of computations.

Strictly speaking, Equation (2.2) gives the number of *unique* correlation results or half of the total correlation results – the remaining half can be obtained by simply reversing the results from the first half. The latter issue is caused by the following property of correlation: correlation of x[k] with y[k] is not the same as correlation of y[k] and x[k]. So, putting down mathematical notation of correlation of y[k] with x[k]:

$$r_{yx}[n] = \sum_{k=-\infty}^{\infty} x[k]y[k-n] = \sum_{l=-\infty}^{\infty} y[l+n]x[l] = r_{xy}[-n]$$

(2.3)

Thus,  $r_{yx}[n]$  is obtained by time-reversing sequence  $r_{xy}[n]$ .

#### 2.2.2 Digital Correlators

As mentioned above, the number of lags is an important feature defining the resolution capabilities of a correlator. The higher the number of lags, the better a correlator can "tell" how similar two signals are to each other. In reality, the number of lags is set by the application's requirements and defines the number of multiply-and-accumulate and multiply-and-add computations. The latter statement is true for *digital correlators*, ie correlators that work with a stream of digitised samples x[n] from an analog output x(t). Two general types of digital correlators are distinguished:

- Lag or XF Correlator

- FX Correlator

In the lag or XF correlator Fourier transform to the frequency domain is performed *after* cross multiplication of signals. The number of channels in such correlators is an integral power of two with the signals' bandwidths also divisible by two to be compatible with digital computing techniques (Thompson et al., 2001a).

Whereas in the FX correlator Fourier transform is performed *before* cross multiplication of signals. Therefore, the total number of operations on the FX correlator is proportional to the number of antennas or more correctly signals coming from these

antennas, whereas in the XF correlator the amount of computation is proportional to the number of antenna (signal) pairs. Hence, the FX correlators are more economical in terms of hardware requirements especially for a considerable number of signals (Thompson et al., 2001b).

#### 2.2.3 Implementations of Correlators

Correlators can be implemented in hardware or software. Normally, hardware correlators are designed and manufactured for a certain and specific application and are implemented in Very Large-Scale Integrated (VLSI) circuits. The CABB Hardware Correlator (Ferris, 2006) is an example of a hardware correlator. This correlator has a complex and very large-scale architecture comprising a number of VLSIs, multiplexers, accumulators, filter banks and other devices. It is utilized in Australia Telescope Compact Array to process signals from six 22 m. antennas of Australia Telescope Compact Array. In addition, FPGAs are used in this correlator as well – to produce different configurations of filter banks.

As for software correlators, they are implemented as a set of libraries or computer programs to perform the designated task: correlation of a given set of signals. Amongst known and acknowledged software correlators the following need to be mentioned:

K5 Software Correlator (Imai, Koyama, & Kondo, 2005) is probably one of the most famous correlators implemented in software. Currently the K5 correlator is involved in the VERA project in Japan and furthermore in collaborative work of Korea and Japan in the project "East Asian Correlator" in Seoul (Kawaguchi, Kobayashi, & Oyama, 2006). K5 is an FX correlator.

Swinburne University of Technology has another software-based correlator. Initially this correlator was XF-type (West, 2004) but it was considered slow and the recently new FX correlator DiFX has been implemented and tested (A. B.T. Deller, Tingay, Bailes, & West, 2007). Both correlators have been implemented on the Linux parallel high-performance parallel cluster utilizing the Message Passing Interface (MPI) standard for process-to-process communications. There was a reported intention to explore hybrid architecture (ie comprising FPGA and Swinburne cluster) within this FX correlator (A. Deller, 2005).

The Jet Propulsion Laboratory of California Institute of Technology designed Softc software correlator (Lowe, 2004). Launched as one of the many test programs to replace an outdated hardware correlator Block I in the Delta-Differenced One-way

Range (DeltaDOR) spacecraft navigation system, Softc underwent a lot of changes and finally was employed in Mars Odyssey, Mars Exploration Rover, Deep Space 1 and other missions. It has significant processing accuracy (not less than  $10^{-13}$ ); it can correlate 1, 2, 4, and 8-bit sampled data, upper, lower, or double sideband data and data using one of either two encoding schemes.

Software correlators are known for their flexibility and possible high spectral resolution along with broad bandwidth (A. B T. Deller et al., 2007). This is achieved by employing high-performance computer systems, eg clusters, massive-parallel computing systems (MPCS or MPC), etc. A cluster is an interconnected group of computers working together as a single computer. The backbone of the clusters is high performance computing units, ie *nodes*. Contemporary clusters involved in high-end digital signal processing applications are considerably complex and elaborate systems with multiple-level architectures and high-speed interconnects. MPC systems are computer systems that include multiple independent processing units running in parallel. Examples of MPC computers include Blue Gene and Earth Simulator amongst others.

The international TOP500 list encompasses the 500 fastest and most powerful computing systems around the world (www.top500.org). As of November 2007, the top supercomputer is the Department of Energy's IBM BlueGene/L system in USA with a performance of nearly 500 TFlops. Another BlueGene/L computer located at the University of Groningen performs correlation tasks in a Low Frequency ARay (LOFAR) project. It consists of 12,288 700 MHz dual PowerPC 440 cores yielding 34.4 TFlop/s of correlation performance (Romein, Broekema, Meijeren, Schaaf, & Zwart, 2006a).

Nevertheless, such performance comes at a price – development time and maintenance cost balance this substantial computational power. With BlueGene/L's power consumption of 27.6 kW per rack (IBM Corporation, 2006) the LOFAR's six-rack supercomputer consumes 165.6 kW per hour. Besides, the estimated development time is one man-year (Romein, Broekema, Meijeren, Schaaf, & Zwart, 2006b). One of the reported issues with the LOFAR's correlators is the lack of the high bandwidth in BlueGene crucial for streaming DSP applications and overall necessity of faster intercommunication between the cores. Moreover, software correlators require substantial debugging and testing of the code: "eliminating of processing errors and inaccuracies" was one of the "greatest hurdles" in Softc correlator implementation

(Lowe, 2004). Developing, debugging and testing can be generalised as one of the greatest hurdles for all high-performance DSP systems.

Along with the considerable complexity of developing high-performance DSP systems go their relevant energy requirements. At the Ninth International Conference on Parallel and Distributed Computing, Applications and Technologies (PDCAT'08), Pete Beckman from Argonne National Laboratory in his keynote speech made a strong point about the power consumption requirements of contemporary and future supercomputers (Beckman, 2008). In particular, it was predicted that within years the power consumption of a computational system would become the most determinative characteristic. In time, increasing the processing capabilities by increasing the operational frequency and adding additional transistors (Moore's law), depleted itself and gradually diverted to multi-core and parallel execution of the algorithms, where currently most of the research and development work is carried out. In turn, the same is envisioned for parallel operation – parallelisation of the applications and algorithms will eventually exhaust with Flops per Watt ratio becoming the systems' performance measuring unit. Therefore, with power requirements becoming one of the most significant factors additional constraints are laid upon the development of highperformance DSP systems and, most importantly, on the technologies applied in these systems.

## 2.3 DSP Technologies

#### 2.3.1 The Performance Requirements of the DSP Applications

The number of mathematical calculations involved in the aforementioned high-end DSP applications is extremely high. For instance, to perform only a 1,024-point FFT yields 10,240 complex multiplications and additions per operational cycle. Moreover, to provide trustworthy data, a radio telescope observing a celestial phenomenon has to employ FFT with even higher resolution as well as a number of other operations, eg correlation of wideband radio-frequency signals, thus yielding even higher number of computations. On top of that, any DSP application, whether it is an image processing routine or telecommunication operation, demands these computations be executed in a rapid manner.

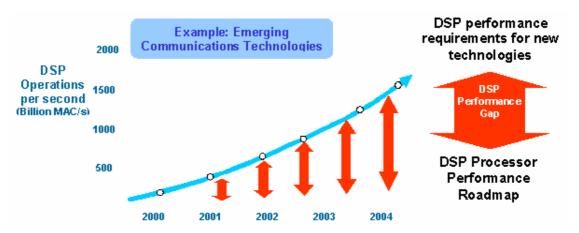

Besides, relentlessly expanding requirements of today's electronic systems keep pushing the resources contemporary DSP instrumentation towards and over the verge of depletion. Figure 2.3 illustrates the performance gap that has emerged in the communication industry between increasing algorithm complexity originated from recent "standards revolution" and existing processing architectures.

Figure 2.3. The DSP Performance Gap in Communications Industry (Ganousis, 2004)

So, how can one approach the ever-growing demands of the DSP field? The most universal approach to meet the substantial and constantly growing requirements of highend DSP applications is to increase the processing power of computational units (CPUs, DSPs, ASICs, etc).

This has a number of limitations and drawbacks such as:

- High power consumption, which in turn leads to necessity of efficient power dissipation;

- Complexity of accommodating a large number of transistors in a single chip,

which are growing with each year according to Moore's Law;

- High market costs.

Hence, this is not always feasible to cover the requirements of a certain high-end DSP application by simply involving more computational power (units) due to the hardware constraints in contemporary tools. Therefore, the search focus has to be shifted towards renovating or enhancing the existing apparatuses or creating new ones. The next sections cover the most common tools available in the DSP field.

#### 2.3.2 Digital Signal Processors (DSPs)

Currently there is a number of tools in the DSP area. One of the major tools for DSP applications are Digital Signal Processors. DSPs were first created in the late 1970s – S2811 (Nicholson et al., 1978) and Intel's 2920 (Hoff & Townsend, 1979). Although

Intel's device did not have a multiplier, it already had on-chip ADC and DAC – a feature still present in the modern DSPs. The 1980s saw a second generation of DSPs with supported concurrency, multiple buses and on-chip memory. These were added with on-chip floating point operations in the third generation of DSPs in the early 1990s. In the late 1990s multi-processing features, image and video processors and low-power DSPs were introduced.

Today DSPs are produced by semiconductor vendors such as Texas Instruments, Analog Devices, Motorola and others. Contemporary top-level DSPs are capable of achieving substantial speeds – for example the high-performance multi-core TMS320C6474 from Texas Instruments can achieve up to 24,000 million instructions per second (MIPS) or 24,000 16-bit MMACs per cycle (Texas Instruments Inc., 2008). This DSP is also equipped with a 16/32-bit DDR2-667 Memory Controller, EDMA3 Controller, 1000 Mbps Ethernet MAC interface, two 1x Serial RapidIO Links and many other peripheries.

In general, DSPs are a specialized form of microprocessor designed specifically for digital signal processing. Nowadays DSPs have a well-developed tool set – typically a high-level programming language as C++. DSPs perform real-time processing and have fixed hardware architecture with certain set of resources. Hence, DSPs have reconfigurability freedom only to the extent of the programming code running on them. Furthermore, the performance requirements of today's DSP applications have now exceeded the capabilities of even such powerful DSPs as Texas Instruments' TMS320C6474.

Another common platform for performing DSP applications – Application-Specific Integrated Circuits (ASICs) possesses an alternative approach for performing signal processing applications.

### 2.3.3 Application-Specific Integrated Circuits (ASICs)

The inception of Application-Specific Integrated Circuits or more commonly ASICs started in 1980s when the now-defunct Ferranti Company released the first gate-array – Uncommitted Logic Array (ULA). The first Uncommitted Logic Arrays contained only a few thousand gate circuits (transistors, logic gates, and other active devices) and they did not perform any specified function. A particular function of a ULA was configured by adding a final layer of metal interconnects to the ULA thus connecting the elements on the ULA in the desired, customised fashion. The later versions of these early

developments became more complicated with a greater number of gates and in some cases included RAM elements.

Modern ASICs retain the same ideology – they perform only limited sets of tasks laid in them during manufacturing stage. These devices are capable of performing their limited sets of functions faster than general-purpose DSPs. Due to application-specific circuitry ASICs are able to employ high-speed functions of the targeted algorithm in the optimized hardware (Kuo & Lee, 2001). Most commonly ASICs are used for implementing well-tested and well-defined algorithms, eg Reed-Solomon coders in digital subscriber loop (xDSL) modems or stack functionalities of CDMA2000 standard in cell phones.

Depending on the grade of flexibility, three levels of ASICs are distinguished:

- Gate Array is the least customisable. Transistors, gates and other devices are predefined but unconnected no metallization layers exist. A user specifies interconnection between the elements thus defining the function of the device. Today these devices are gradually replaced by structured ASICs where many features are predefined by the manufacturer: IP cores, power and clock sources, etc. This significantly reduces the design time, as a user has to specify much fewer design technicalities.

- Standard cell methodology has a high degree of flexibility. It assumes that the ASIC's design is defined by a user from the cell libraries created by the manufacturer and, therefore, has much less space for mistake than full custom design.

- Full custom design is the most flexible and, therefore, the most expensive and time-consuming approach. It assumes developing an ASIC from transistor level.

Despite that ASICs can perform their specified application faster than general-purpose DSPs, they do posses their own challenges and limitations. The most obvious limitation of ASICs originates from their most prominent strength: hardware optimised for performing dedicated applications means little or, most often, absolutely no degree of algorithm flexibility.

Another challenge with ASICs is that they are configured with hardware description languages (HDL) such as Verilog, VHDL and some other less popular options. These languages are low-level programming languages and differ significantly

from high-level programming languages employed for programming conventional general-purpose DSPs. The challenges of hardware description languages are more broadly discussed in section 3.1.2.

Single DSP or ASIC can be employed as a platform for single or several signal-processing applications. In the case of large-scale high-performance DSP applications, they may be employed as building blocks in sizeable computational systems such as supercomputers, computational clusters, grid computing, etc.

### 2.3.4 High-Performance Computing

For performing large-scale DSP applications, high-performance computing (HPC) systems can be used. HPC systems (supercomputers or computer clusters) comprising multiple computational processors communicate through versatile types of interconnect. The types of DSP applications employed on HPC systems are exceedingly large-scale and include but are not limited to: correlation of wideband RF signals involved in radio observation of celestial objects (eg CABB (Ferris, 2006) or DiFX (A. B T. Deller et al., 2007) Australian correlators), video-centric applications of new generation wireless telecommunications standards, such as wireless videoconferencing, real-time video streaming, etc. (Gentile & Wills, 2004) and many others.

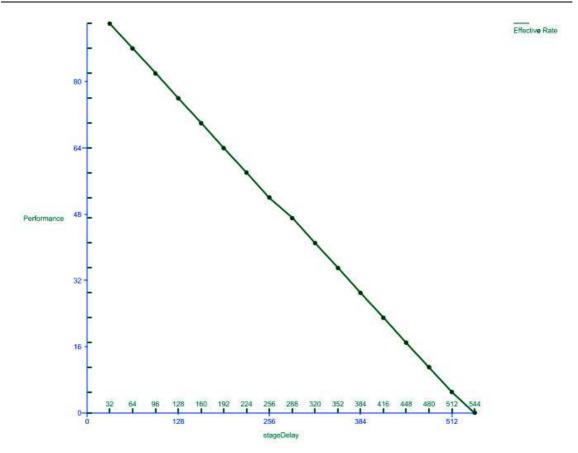

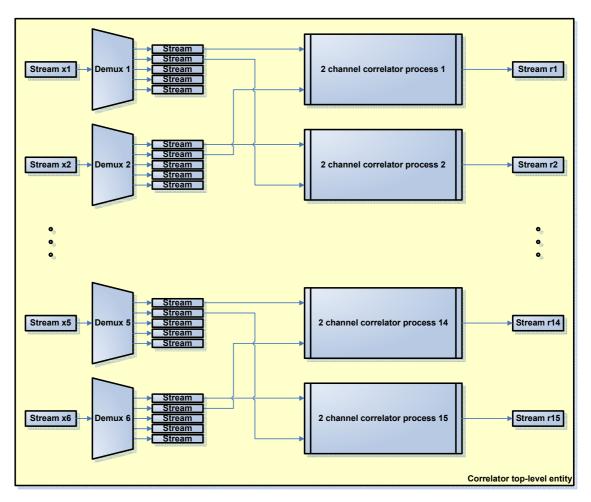

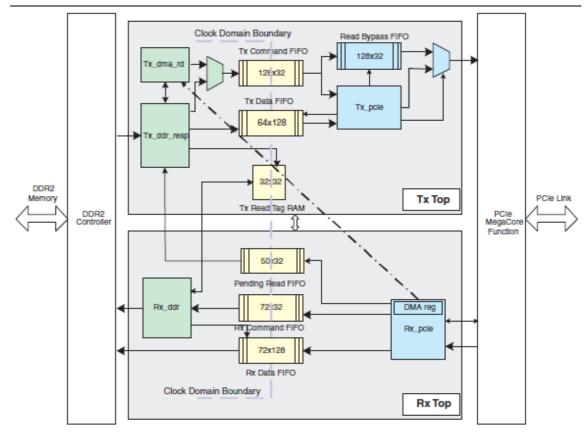

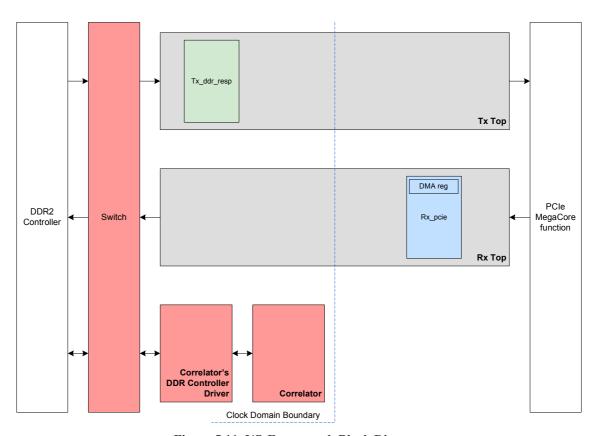

Over the years, the HPC proved to be an effective and sophisticated tool for performing DSP applications. Technologies and tools applied in HPC have significantly developed over the past years – density of transistors on processors (Moore's law), communication speeds and throughputs, number of processors performing one task, uniform memory access with few or no caches, etc. In addition, modern HPC systems are practically linearly scalable.