## **System on Chip (SoC):**

## A Real Time Touch Screen System on Programmable Chip

## Stephen Xu

A thesis submitted in fulfillment of the requirements for the degree of Master of Engineering (ME)

In Electrical and Electronic Engineering

Auckland University of Technology, New Zealand

November 2011

School of Engineering

Primary Supervisor: Dr John Collins

Kaore ko au

E kimi ana,

E hahau ana,

I nga pari ra

Piri nga hakoakoa,

E kau oma tera.

Ka toa atu tera

Ka ao mai te ra

Ki tua.

E I a ha-a!

Seeking, searching, peering,

As on those rocky crags

The sea-hawk sits

And watches for his prey,

Soon will the sun

Rise flaming over the world!

Whakaaraara-pa

From Rauparaha's Ngati-Toa warriors

## **Attestation of Originality**

'I hereby declare that this submission is my own work and that, to the best of my knowledge and belief, it contains no material previously published or written by another person nor material which to a substantial extent has been accepted for qualification of any other degree or diploma of a university or other institution of higher learning, except where certain content is exactly defined in the acknowledgements.'

Stephen Xu

November 2011

### Acknowledgement

I am very grateful to both of my academic supervisors: Dr John Collins and Mark Beckerleg. With your patient mentoring, strict requirements and kind encouragement through all these years, I have become a better person with independent research capability, innovative thinking and consistent motivation from inside.

Dr John Collins has provided invaluable guidance and advice on the architectural and directional level with his broad background in embedded system. And Mark Beckerleg has been a technical mentor and friend in the new technology domain with numerous amounts of help and assistance.

I am also very grateful to all my industry supervisors: Simon Bridger, John Newton and Gordon Macdonald. I am grateful for the research platform which is based on unique technology, aiming at investigating and solving real world limitations and having an impact on the outcome. I have benefited a lot from all my supervisors from different perspectives and I would like to express my sincere appreciation again.

Finally, I am very grateful for the help from technicians in the university and engineers inside the company in terms of system understanding, prototype building and trouble shooting. I would like to thank all my friends and family as well since it has been a long and difficult process.

### **Abstract**

This thesis is involved with the investigation, implementation, verification, validation and optimization of a purpose built on-chip solution customized for a real world touch screen application. A Field Programmable Gate Array based application specific controller has been designed and built in this research as a substitute for a general purpose controller to explore the feasibility and capability of meeting the required system performance while maintaining the minimum consumption of system resources. A variety of new mechanisms, approaches and techniques have been evaluated, developed and applied to different design stages at multiple levels to achieve an overall optimized system outcome.

A dedicated optical imaging acquisition system has been developed with a concurrent control mechanism, faster operational speed and lower signal noise; a customized touch information processing unit has been designed to perform edge detection, object positioning, and touch motion indication with low system latency and highly parallelism; and a computer interface has been built to demonstrate the coherent real-time system performance with visualized validation of results. In the optical based touch screen area, this research presents an original and compact on-chip solution with a significant number of algorithm and method improvements in terms of the touch object detection and localization efficiency as well as touch motion analyzing capability.

The system design has been optimized after establishing the desired functionality to minimize logic resource and memory storage consumption, based on a wide range of techniques with a certain amount of architectural restructuring. The overall economic on-chip resource consumption has been achieved in this research with further consideration for migrating the design into a more application specific high integration density chip in the future for large volume manufacture.

## **Table of Contents**

| Abstract                                                        | 1  |

|-----------------------------------------------------------------|----|

| List of Figures                                                 | V  |

| List of Tables                                                  | ix |

| List of Abbreviations                                           | X  |

| Chapter 1 Background and Introduction                           | 1  |

| 1.1 Background and Requirements Analysis                        | 1  |

| 1.2 Objective and Methodology                                   | 5  |

| 1.3 System Abstraction and Overview                             | 7  |

| Chapter 2 Literature Review                                     | 10 |

| 2.1 Hardware Accelerated Hybrid System                          | 10 |

| 2.1.1 Software-Oriented Hybrid System                           | 10 |

| 2.1.2 Hardware-Oriented Hybrid System                           | 12 |

| 2.1.3 Hardware/Software Co-Design System                        | 15 |

| 2.2 Image Acquisition and Processing                            | 18 |

| 2.3 Field Programmable Gate Arrays                              | 21 |

| 2.4 System on Chip (SoC)                                        | 25 |

| Chapter 3 Touch Screen System on Chip Design and Implementation | 28 |

| 3.1 Introduction                                                | 28 |

| 3.2 Data Acquisition System                                     | 29 |

| 3.2.1 Data Acquisition System Overview                          | 29 |

| 3.2.2 Acquisition Controller                                    | 30 |

| 3.2.4 Analog to Digital Convertor                               | 35 |

| 3.2.5 Universal Serial Bus 2.0                                  | 39 |

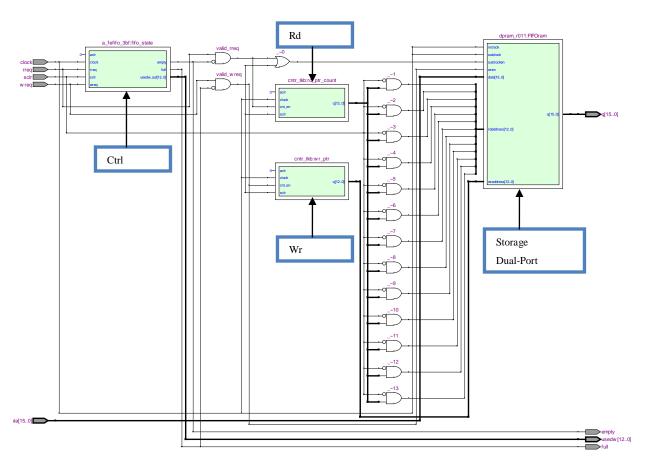

| 3.2.6 System FIFO                                               | 42 |

| 3.2.7 PCB Finalization                                          | 44 |

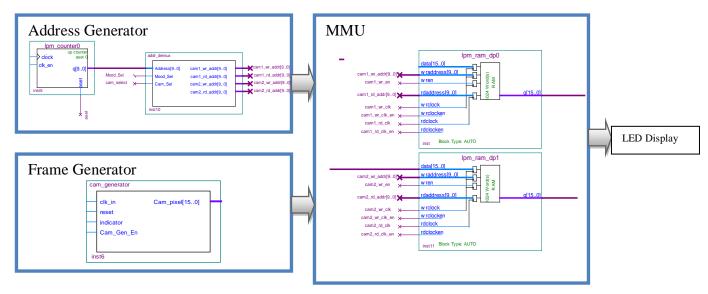

| 3.3 Memory Management Unit (MMU)                                | 46 |

| 3.3.1 Memory Elements Overview                                  | 46 |

| 3.3.2 Memory Management Unit Control Structure                  | 47 |

| 3 3 3 Constrained Memory Management Unit Structure              | 50 |

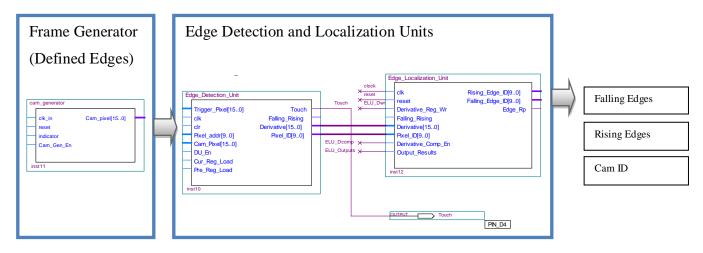

| 3.4 Edge Localization Unit (ELU)                                  | 51 |

|-------------------------------------------------------------------|----|

| 3.4.1 Edge Localization Unit Overview                             | 51 |

| 3.4.2 Edge Detection Unit                                         | 52 |

| 3.4.3 Edge Localization Unit                                      | 53 |

| 3.5 Position Localization Unit (PLU)                              | 55 |

| 3.5.1 Position Localization Mechanism                             | 55 |

| 3.5.2 Position Localization Unit Structure Transformation         | 56 |

| 3.5.4 Position Localization Unit Structure Overview               | 59 |

| 3.5.3 Binary Search Engine                                        | 60 |

| 3.5.4 Triangulation Operator                                      | 61 |

| 3.5.5 Position Localization Unit Registers                        | 61 |

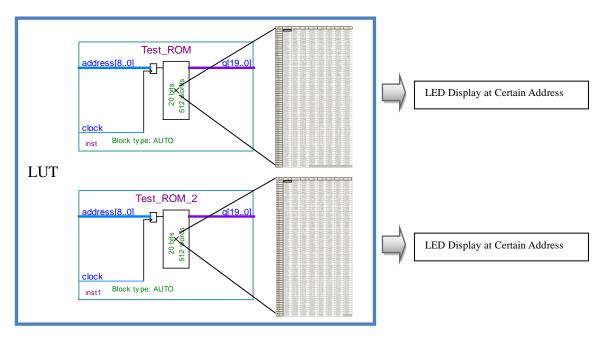

| 3.6 System Look Up Table                                          | 62 |

| 3.7 Normaliser Unit                                               | 65 |

| 3.7.1 Normaliser Operator                                         | 65 |

| 3.7.2 Level Detection Logic                                       | 66 |

| 3.7.3 Normaliser Register                                         | 66 |

| 3.7.4 Norm Comparator                                             | 66 |

| 3.7.5 Gesture Register                                            | 66 |

| 3.8 System Master Controller                                      | 67 |

| 3.8.1 System Master Controller Control Flow                       | 67 |

| Chapter 4 Touch Screen System on Chip Testing Methods and Results | 70 |

| 4.1 Overview                                                      | 70 |

| 4.2 Data Acquisition System Testing Methods and Results           | 70 |

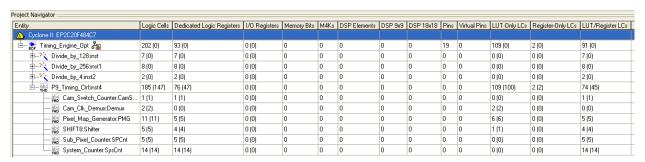

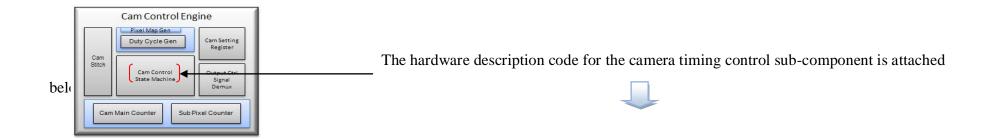

| 4.2.1 Timing Control Engine Testing Method and Results            | 70 |

| 4.2.2 ADC Testing Method and Results                              | 72 |

| 4.2.3 USB Testing Method and Results                              | 73 |

| 4.2.4 Noise Analysis and Results                                  | 74 |

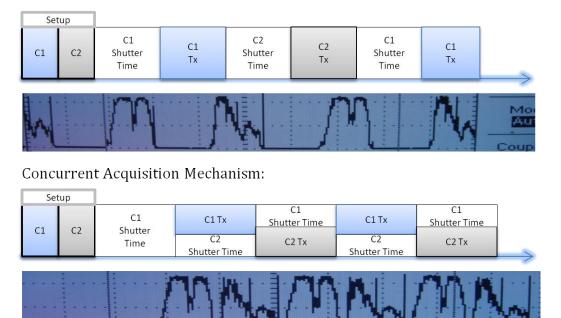

| 4.2.5 Concurrent Acquisition Mechanism Testing Method and Results | 75 |

| 4.3 Processing Unit Testing Methods and Results                   | 76 |

| 4.3.1 Memory Management Unit Testing Method and Results           | 77 |

| 4.3.2 System LUT Testing Method and Results                       | 78 |

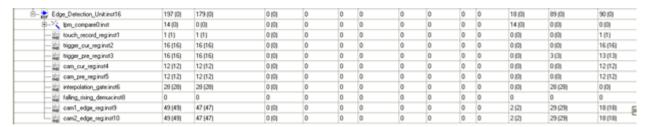

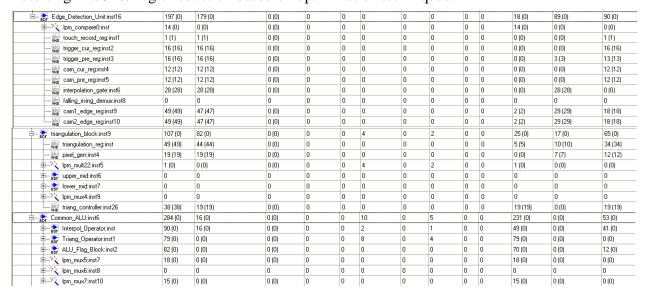

| 4.3.3 Edge Localization Unit Testing Method and Results                       | 78  |

|-------------------------------------------------------------------------------|-----|

| 4.3.4 Normaliser Testing Method and Results                                   | 82  |

| 4.3.5 Position Localization Unit Testing Method and Results                   | 83  |

| 4.4 Complete Real-Time System Testing Results                                 | 84  |

| Chapter 5 Hardware Touch Screen System Optimization                           | 87  |

| 5.1 System Optimization Overview                                              | 87  |

| 5.2 Top-Level Architecture Optimization                                       | 88  |

| 5.3 Behavioral and Functional Level Optimization                              | 89  |

| 5.3.1 Algorithm Evaluation (Alteration)                                       | 89  |

| 5.3.2 Memory Resource Reduction                                               | 95  |

| 5.3.3 Pipeline Rolling and Resource Sharing                                   | 96  |

| 5.3.4 Iterative Approach and Time-Division-Multiplexing (TDM)                 | 101 |

| 5.3.5 Retiming and Register Balancing                                         | 104 |

| 5.3.6 Multiplexer Resource Reduction                                          | 105 |

| 5.3.7 State Machine Optimization                                              | 107 |

| 5.4 Floor Planning                                                            | 109 |

| 5.5 Reducing Power Dissipation                                                | 111 |

| Chapter 6 Touch Screen System Optimization Results                            | 112 |

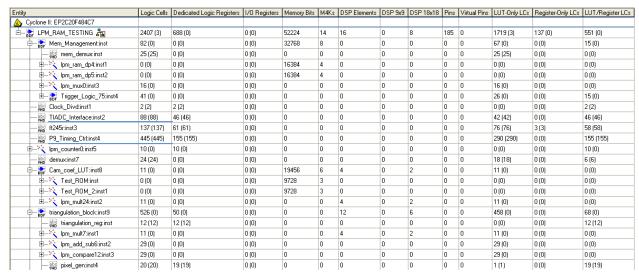

| 6.1 Resource Optimization Results Original Version                            | 112 |

| 6.2 Resource Optimization Results Memory-Oriented Optimization                | 113 |

| 6.3 Resource Optimization Results Logic Elements-Oriented Optimization        | 115 |

| 6.3.1 Algorithm alteration based logic optimization                           | 115 |

| 6.3.2 Resource sharing, iterative approach and TDM based optimization results | 115 |

| 6.3.3 Multiplexer restructuring algorithm based logic reduction results       | 118 |

| 6.3.4 Retiming and Register Balancing based optimization results              | 118 |

| 6.4 Resource Optimization Conclusion                                          | 120 |

| 6.5 Optimized Chip Floor Planning Result                                      | 121 |

| Chapter 7 Discussion and Conclusion                                           | 122 |

| 7.1 Conclusion                                                                | 122 |

| 7.2 Future Work                                                               | 125 |

| Deferences                                                                    | 127 |

| Appendices     | 13 | 1 |

|----------------|----|---|

| 1 1pp en arees |    | - |

# **List of Figures**

| Figure 1 Simplified Optical Imaging Based Touch Screen System                     | 2  |

|-----------------------------------------------------------------------------------|----|

| Figure 2 Left and Right Line Scan Sensors Waveform                                | 2  |

| Figure 3 Left and Right Line Scan Sensors Waveform with Single Touch              | 2  |

| Figure 4 Simplified System Block Diagram                                          | 7  |

| Figure 5 Software-Oriented Hybrid System                                          | 11 |

| Figure 6 Hardware-Oriented Hybrid System                                          | 13 |

| Figure 7 Hardware Software Co-design Approach                                     | 16 |

| Figure 8 SRAM Based Logic Element Structure                                       | 22 |

| Figure 9 Flash Based Logic Cell Structure                                         | 23 |

| Figure 10 Performance Benchmark of Vision Based Algorithms on Different Platforms | 24 |

| Figure 11 Stereo-vision and K-means Clustering Algorithms on Different Platforms  | 25 |

| Figure 12 Data Acquisition System Block Diagram                                   | 29 |

| Figure 13 Acquisition Controller Block Diagram                                    | 30 |

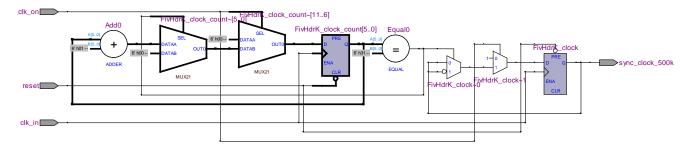

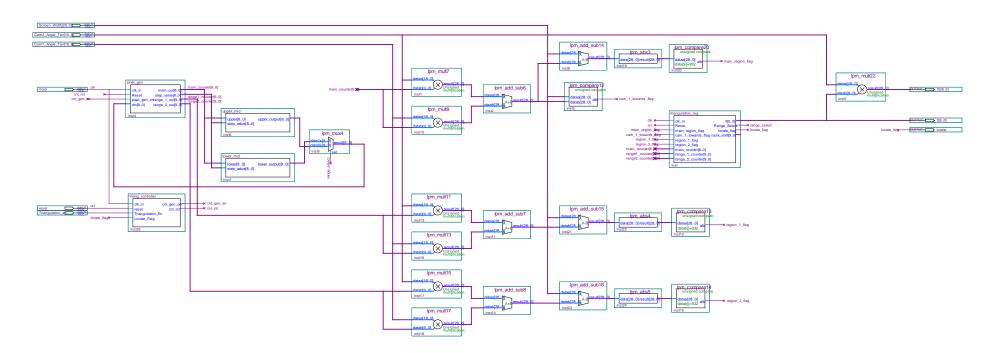

| Figure 14 Clock Divider RTL Structure                                             | 32 |

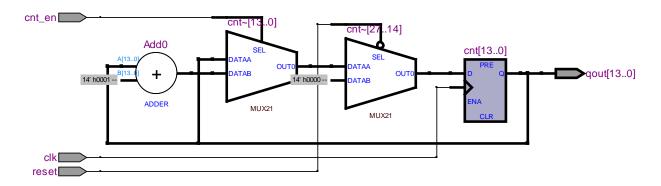

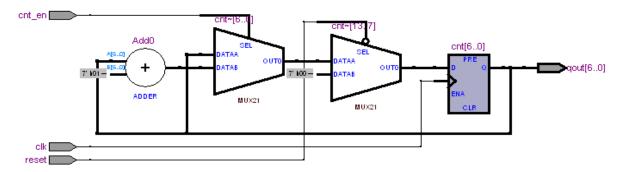

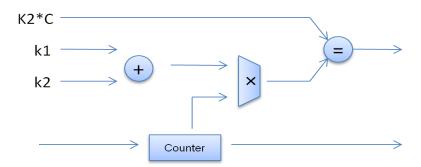

| Figure 15 Acquisition Engine Counter Module RTL Structure                         | 33 |

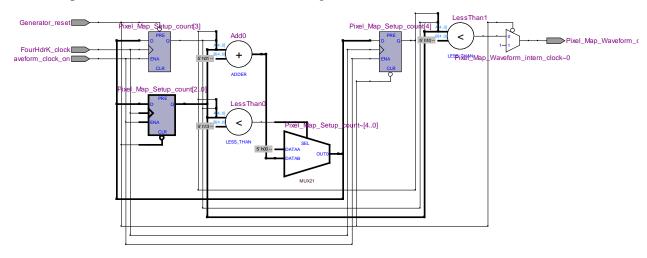

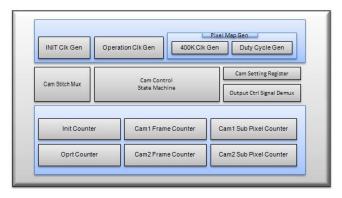

| Figure 16 Pixel Map Generator RTL Structure                                       | 34 |

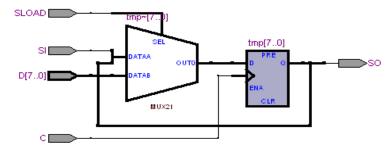

| Figure 17 Acquisition Engine Shift Register RTL Structure                         | 34 |

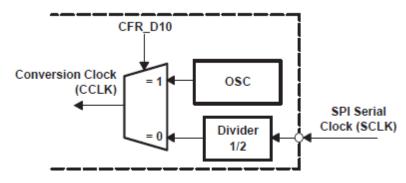

| Figure 18 ADC Chip Conversion Clock Block Diagram                                 | 35 |

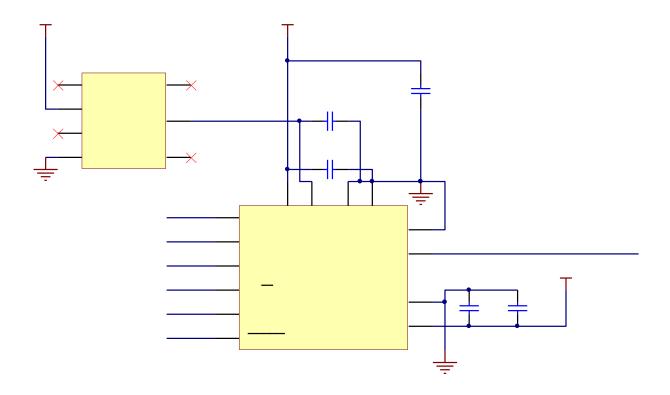

| Figure 19 ADC Chip Configuration Circuit                                          | 36 |

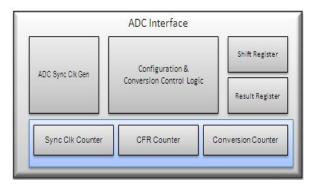

| Figure 20 ADC Interface Block Diagram                                             | 37 |

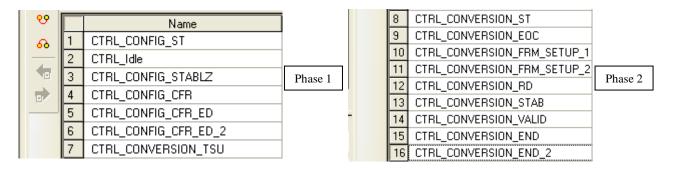

| Figure 21 ADC Counter Module RTL Structure                                        | 38 |

| Figure 22 ADC Register RTL Structure                                              | 38 |

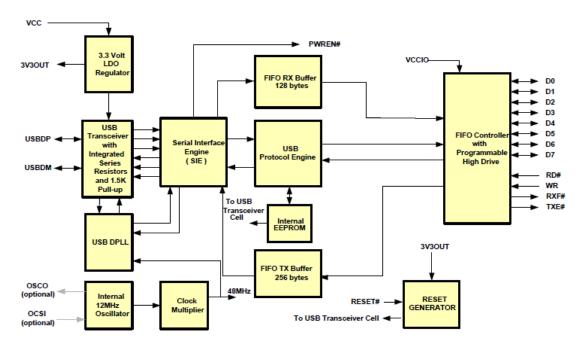

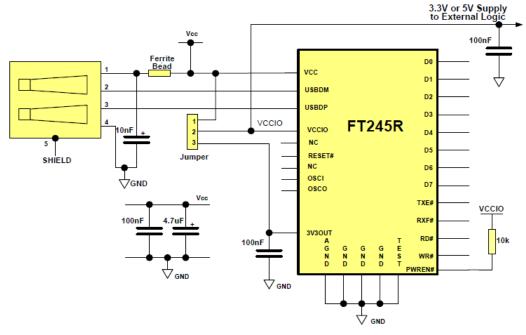

| Figure 23 USB Chip Block Diagram                                                  | 39 |

| Figure 24 USB Chip Configuration Circuit                                          | 40 |

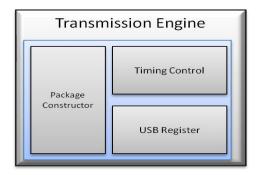

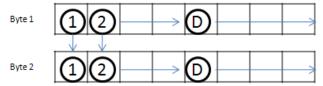

| Figure 25 Transmission Engine Block Diagram                                       | 41 |

| Figure 26 USB Package Constructor Structure                                       | 41 |

| Figure 27 System FIFO RTL Structure                                                    | 42 |

|----------------------------------------------------------------------------------------|----|

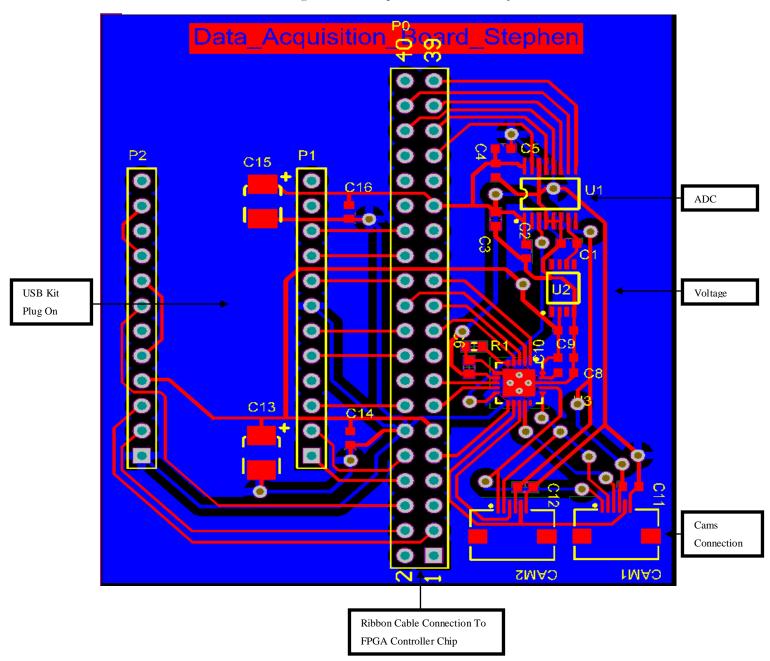

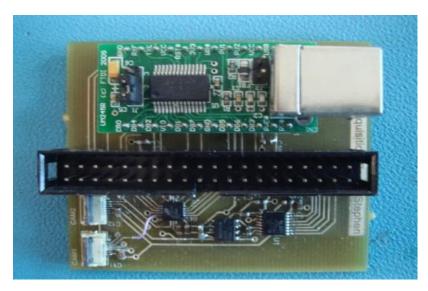

| Figure 28 Data Acquisition Board PCB Layout                                            | 44 |

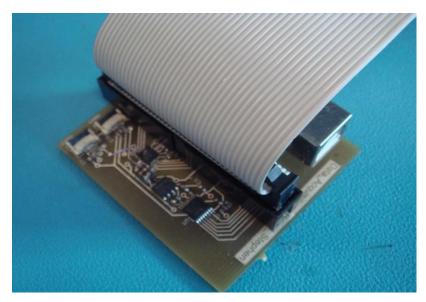

| Figure 29 Data Acquisition Board Physical View                                         | 45 |

| Figure 30 Data Acquisition Board Connected to Dev Board                                | 45 |

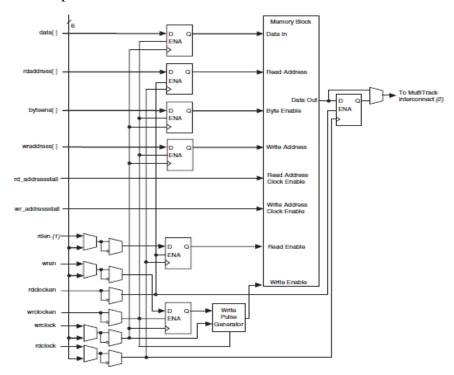

| Figure 31 Dual-Port Ram Read/Write Operation Structure                                 | 47 |

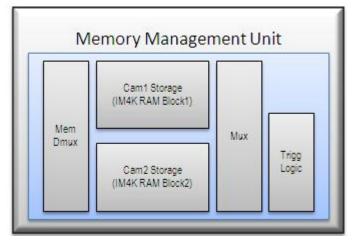

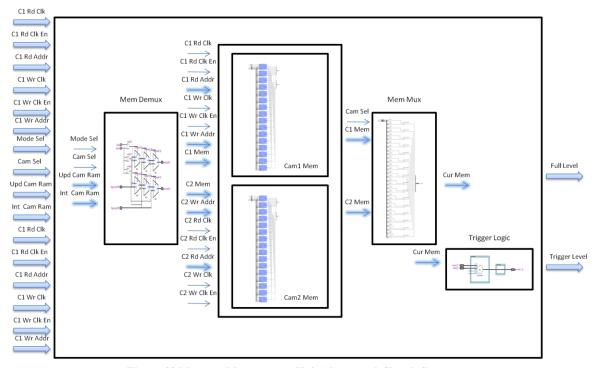

| Figure 32 Memory Management Unit Block Diagram                                         | 48 |

| Figure 33 Memory Management Unit Abstracted Circuit Structure                          | 48 |

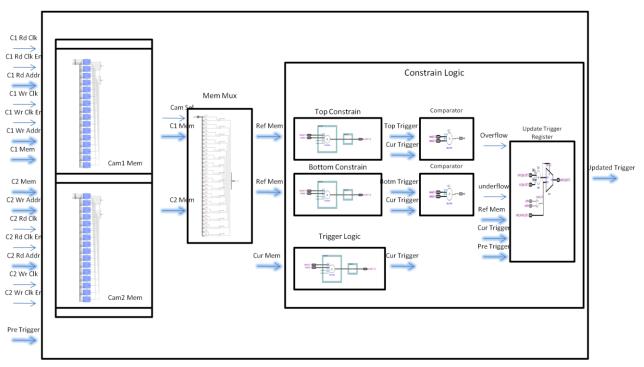

| Figure 34 Constrained Memory Management Unit Abstracted Circuit Structure              | 50 |

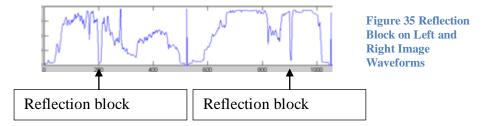

| Figure 35 Reflection Block on Left and Right Image Waveforms                           | 51 |

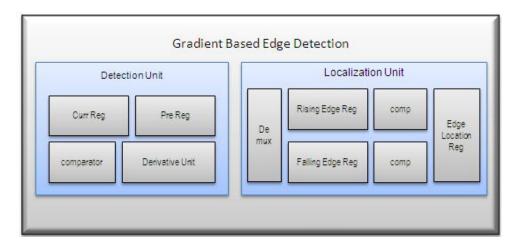

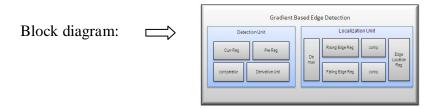

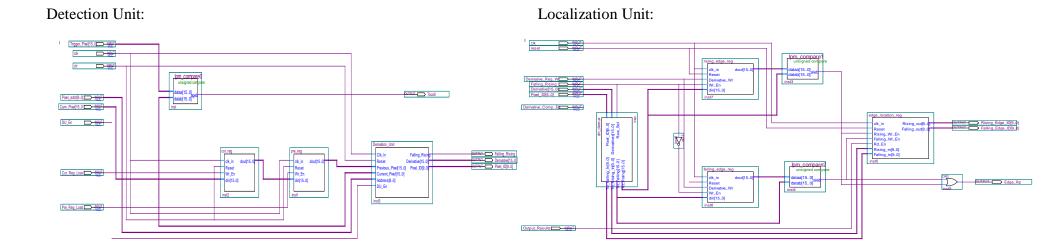

| Figure 36 Gradient Based Edge Detection Block Diagram                                  | 52 |

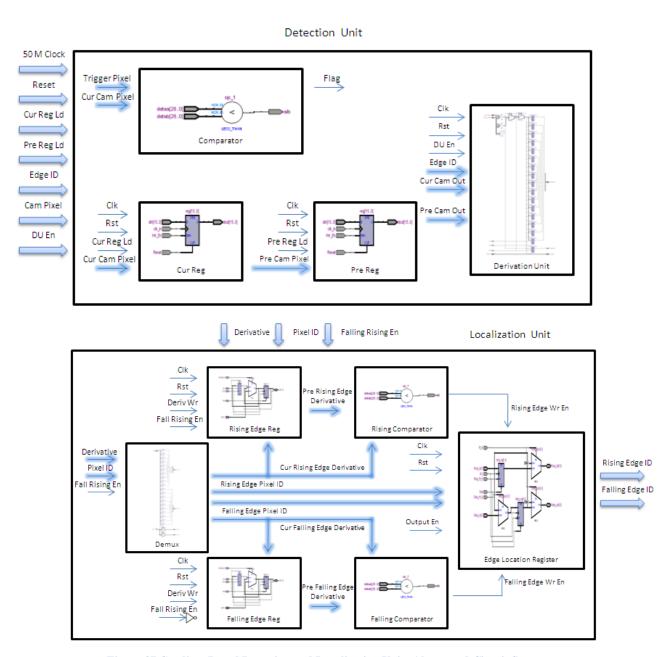

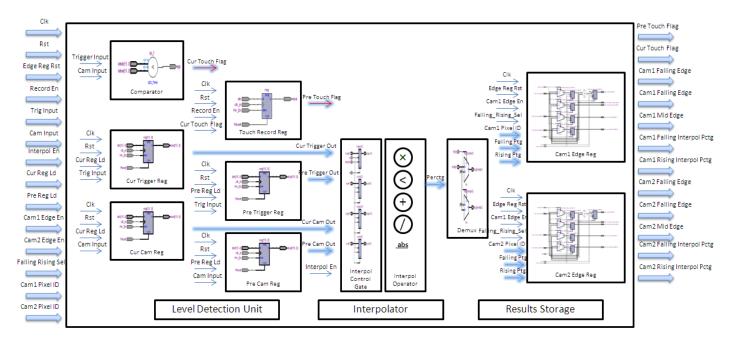

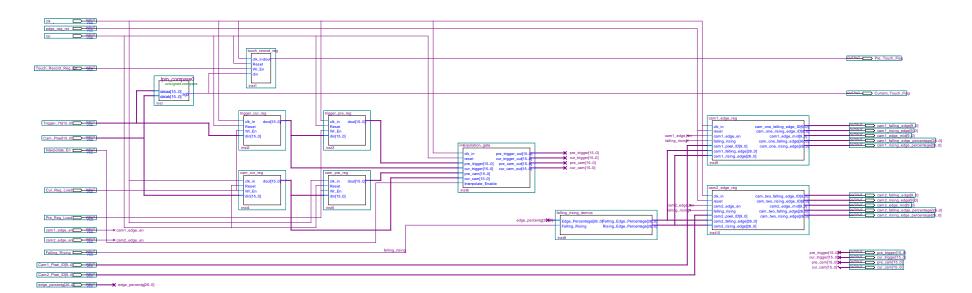

| Figure 37 Gradient Based Detection and Localization Units Abstracted Circuit Structure | 53 |

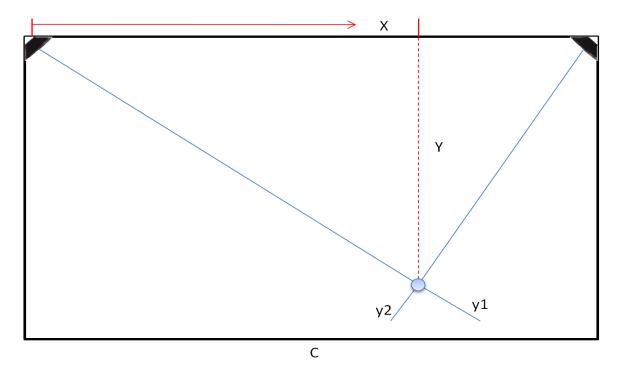

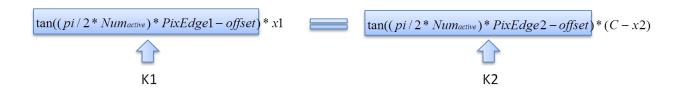

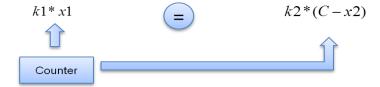

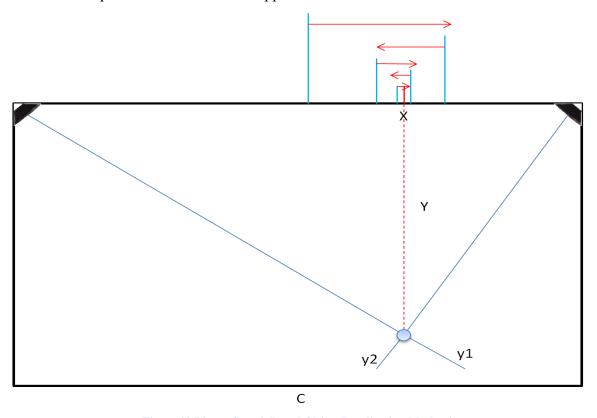

| Figure 38 Position Localization Mechanism Illustration                                 | 55 |

| Figure 39 Binary Search Based Object Localization Mechanism                            | 58 |

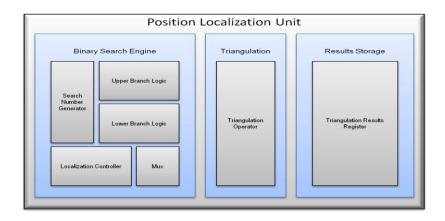

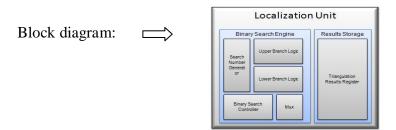

| Figure 40 Position Localization Unit Block Diagram                                     | 59 |

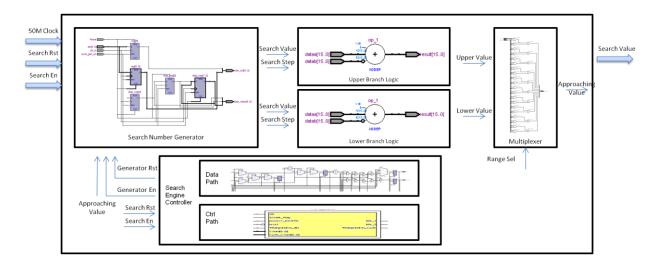

| Figure 41 Binary Search Engine Abstracted Circuit Structure                            | 60 |

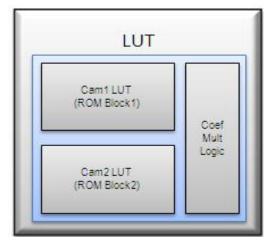

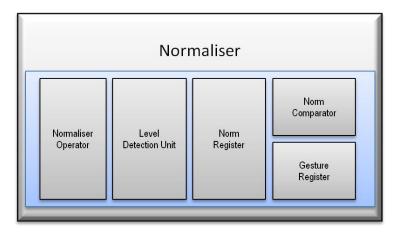

| Figure 42 Look Up Table Block Diagram                                                  | 62 |

| Figure 43 Look up Table Abstracted Circuit Structure                                   | 63 |

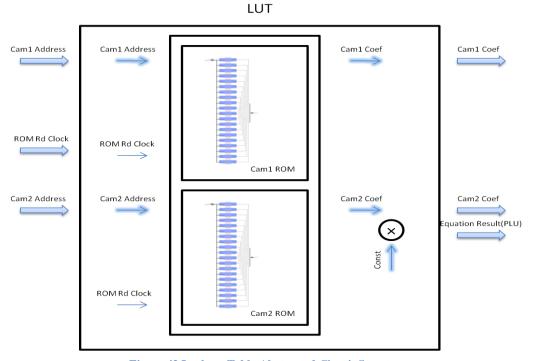

| Figure 44 Look up Table Correspondence Value                                           | 64 |

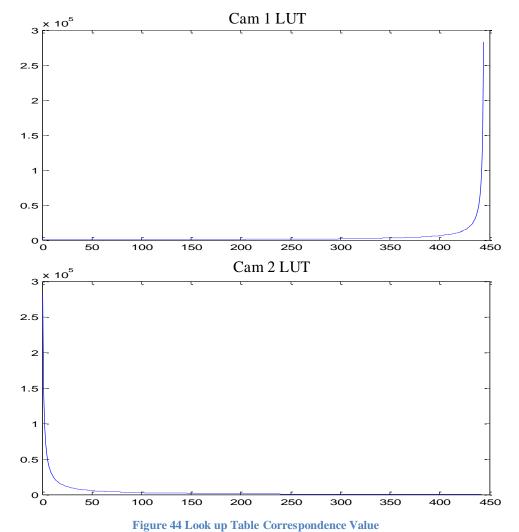

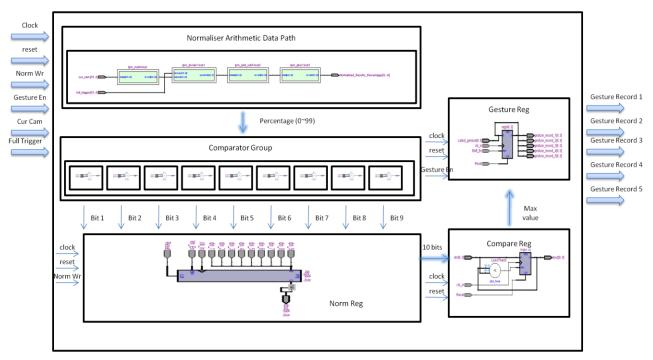

| Figure 45 Normaliser Block Diagram                                                     | 65 |

| Figure 46 Normaliser Abstracted Circuit Structure                                      | 66 |

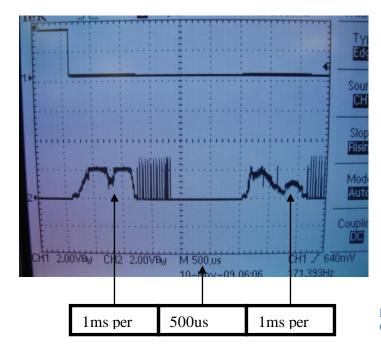

| Figure 47 Acquisition Timing Control Testing Result                                    | 70 |

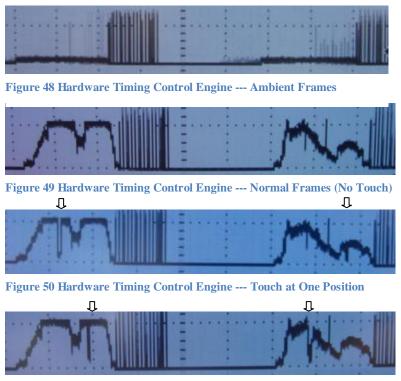

| Figure 48 Hardware Timing Control Engine Ambient Frames                                | 71 |

| Figure 49 Hardware Timing Control Engine Normal Frames (No Touch)                      | 71 |

| Figure 50 Hardware Timing Control Engine Touch at One Position                         | 71 |

| Figure 51 Hardware Timing Control Engine Touch at another Position                     | 71 |

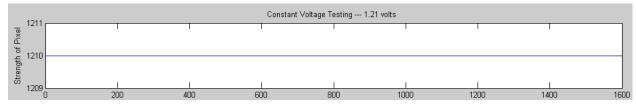

| Figure 53 ADC Testing Results Constant Voltage Input                                   | 72 |

| Figure 52 Figure 36 Acquisition Timing Control Testing Result 900K                     | 72 |

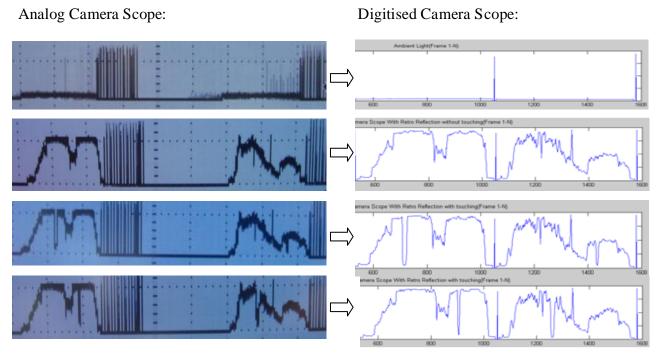

| Figure 54 Data Acquisition System Digitization Result                                  | 73 |

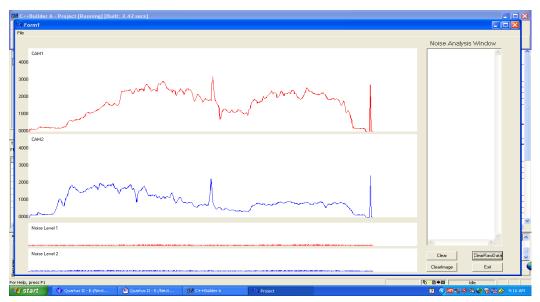

| Figure 55 PC Monitor Interface                                                         | 74 |

| Figure 56 Data Acquisition System Noise Analysis Result                                | 75 |

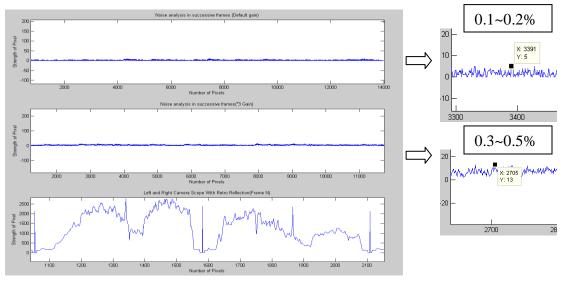

| Figure 57 Concurrent Acquisition Mechanism Testing Result                              | 76 |

| Figure 58 Memory Management Unit Testing Structure                                      | 77       |

|-----------------------------------------------------------------------------------------|----------|

| Figure 59 System Look up Table Testing Structure                                        | 78       |

| Figure 60 Edge Detection and Localization Units Testing Structure                       | 79       |

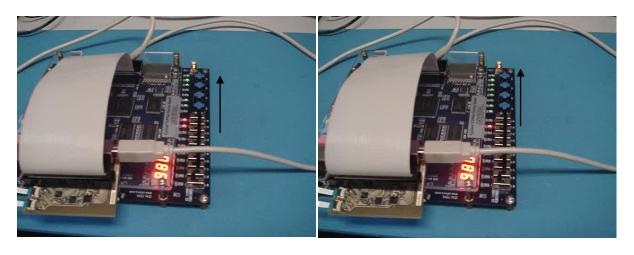

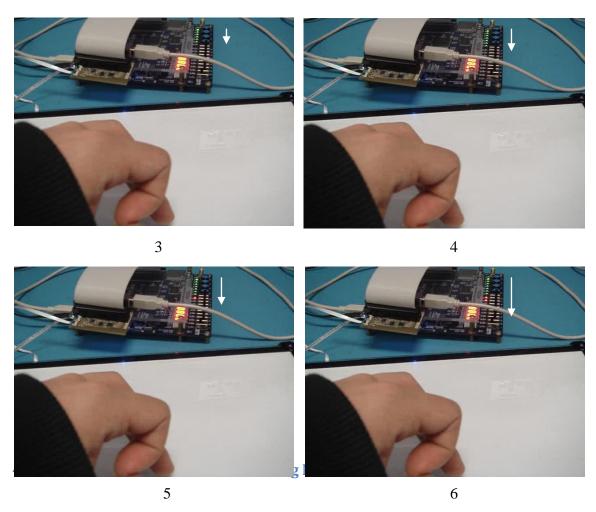

| Figure 61 Edge Localization Unit Real Time Testing Result (Edge Up)                     | 80       |

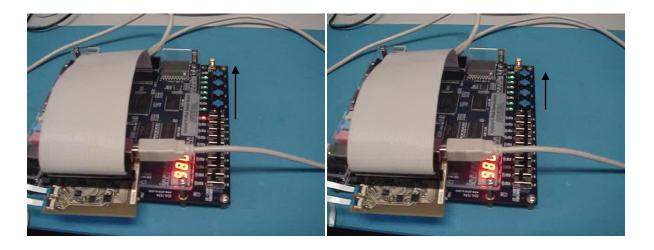

| Figure 62 Figure 50 Edge Localization Unit Real Time Testing Result (Edge Down)         | 82       |

| Figure 63 Normaliser Testing Result (Touch Down)                                        | 83       |

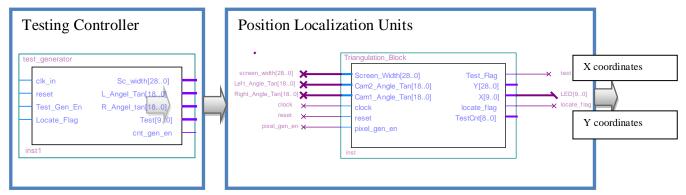

| Figure 64 Position Localization Unit Testing Structure                                  | 84       |

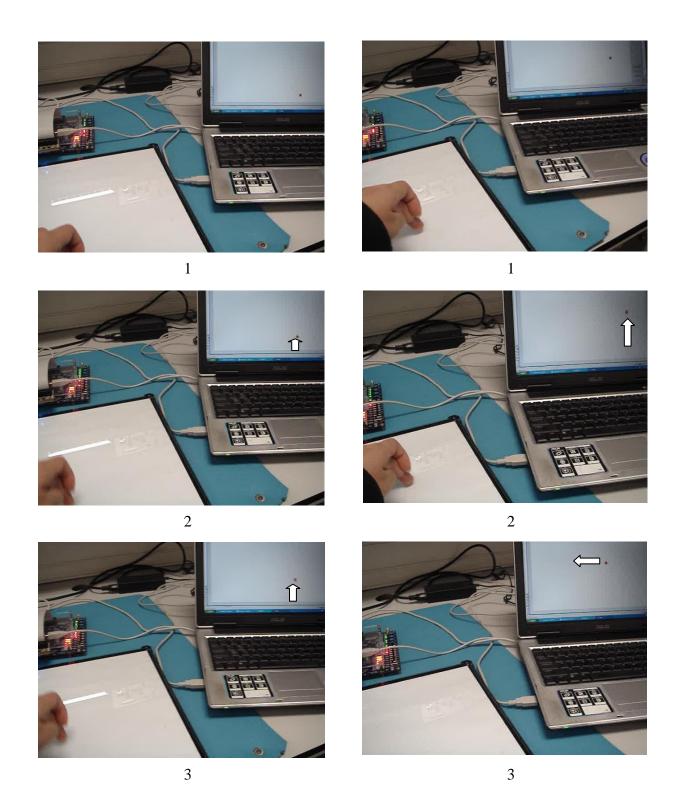

| Figure 65 Real Time Touch Screen System Testing Results (Drawing Straight Line, rectain | ngle) 86 |

| Figure 66 Original Top Level System Flow                                                | 88       |

| Figure 67 Optimized Top Level System Flow                                               | 88       |

| Figure 68 Linear approximation sub-pixel detection of Hussmann and Ho's system          | .Error!  |

| Bookmark not defined.                                                                   |          |

| Figure 69 Dynamic Linear Approximation Sub-Pixel Detection Based on Real Camera Sc      | ope91    |

| Figure 70 Trigger Level Based Edge Localization Block Diagram                           | 92       |

| Figure 71 Trigger Level Based Edge Localization Abstracted Circuit Structure            | 92       |

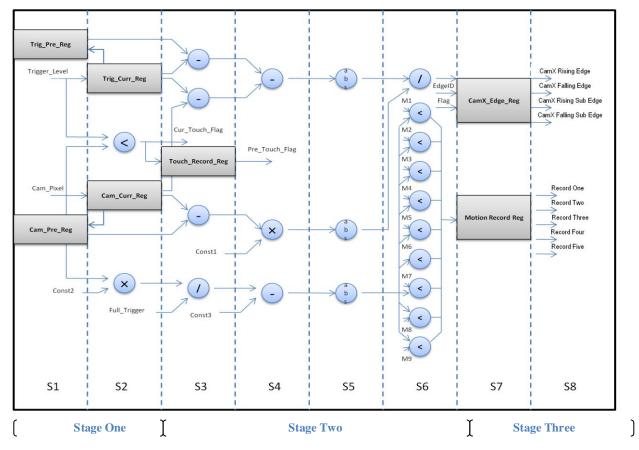

| Figure 72 Pipelined Data Flow of Edge Detection and Localization Unit with Nomaliser    | 94       |

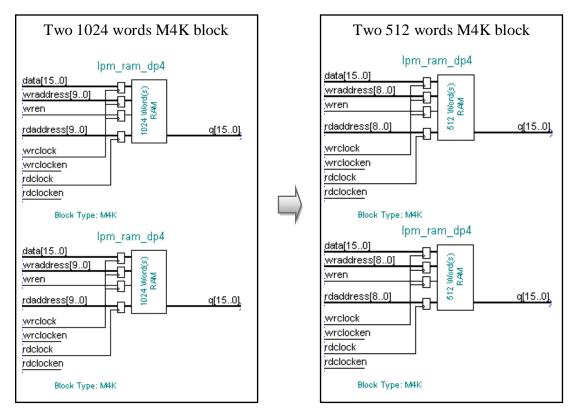

| Figure 73 Memory Resource Optimization Illustration                                     | 95       |

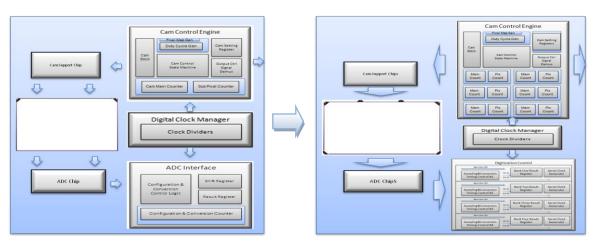

| Figure 74 Data Acquisition Engine Block Diagram without Optimization                    | 97       |

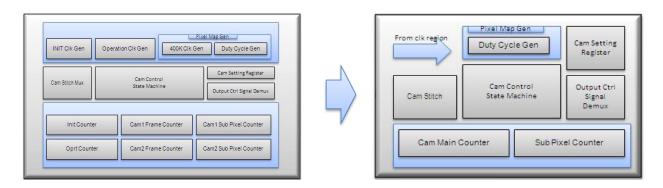

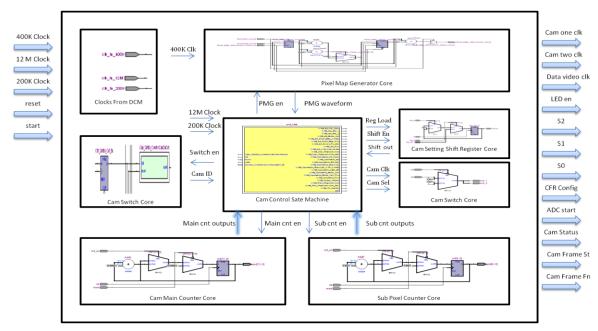

| Figure 75 Optimized Data Acquisition Engine Block Diagram                               | 97       |

| Figure 76 Optimized Acquisition Engine Abstracted Circuit Structure                     | 98       |

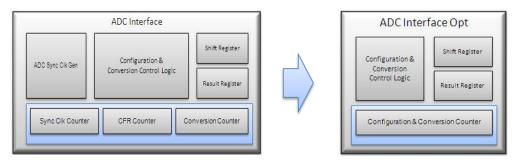

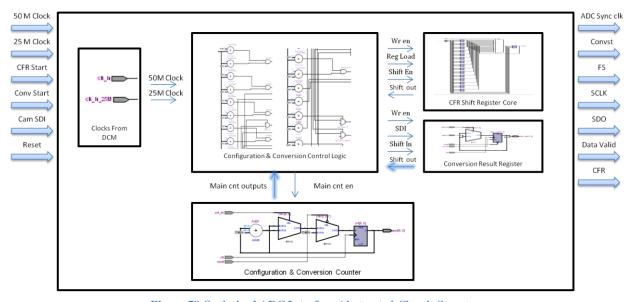

| Figure 77 Optimized ADC Interface Block Diagram                                         | 99       |

| Figure 78 Optimized ADC Interface Abstracted Circuit Structure                          | 99       |

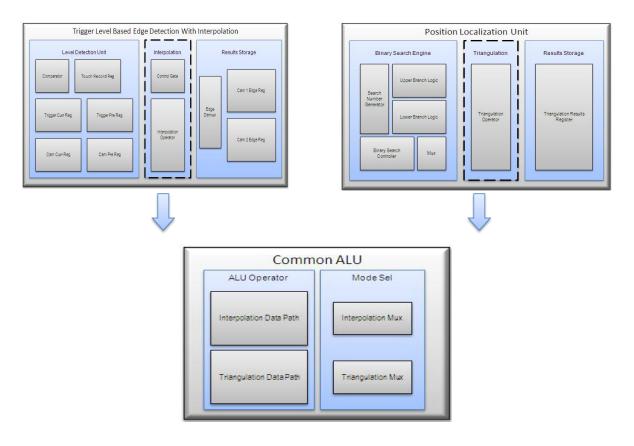

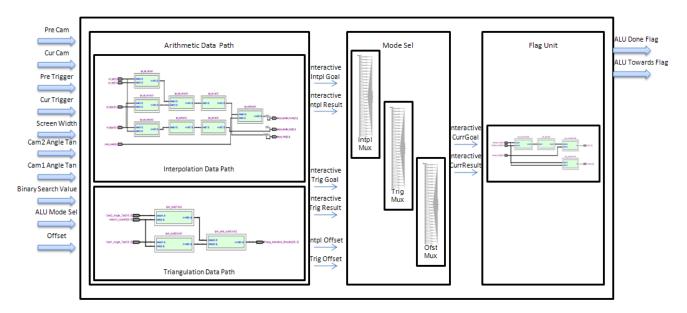

| Figure 79 Arithmetic Resource Sharing Common ALU                                        | 100      |

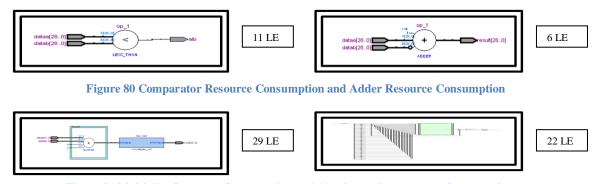

| Figure 80 Comparator Resource Consumption and Adder Resource Consumption                | 101      |

| Figure 81 Multiplier Resource Consumption and Absolute value operator Consumption       | 101      |

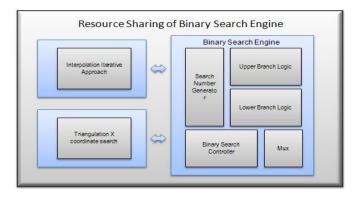

| Figure 82 Resource Sharing of Binary Search Engine                                      | 102      |

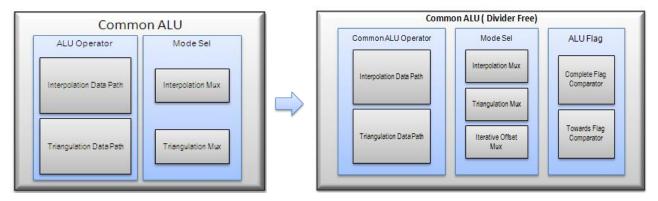

| Figure 83 Divider Free Arithmetic Logic Unit                                            | 102      |

| Figure 84 Common ALU Abstracted Circuit Structure                                       | 103      |

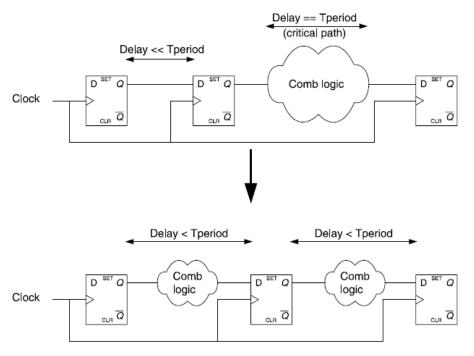

| Figure 85 Retiming and Register Balancing Illustration                                  | 104      |

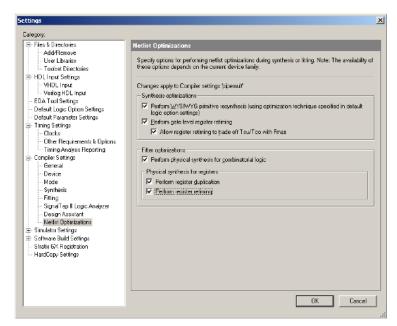

| Figure 86 Retiming and Register Balancing Option                                        | 105      |

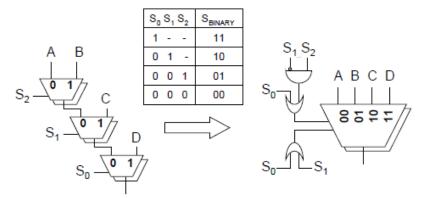

| Figure 87 Multiplexer Restructuring Algorithm Compression                               | 106      |

| Figure 88 Multiplexer Restructuring Algorithm Balancing          | 106 |

|------------------------------------------------------------------|-----|

| Figure 89 Original Acquisition Controller Data and Control Path  | 108 |

| Figure 90 Optimized Acquisition Controller Data and Control Path | 108 |

| Figure 91 Physical Chip Overview                                 | 109 |

| Figure 92 Logic Element Configuration                            | 109 |

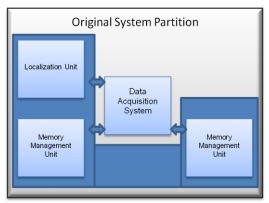

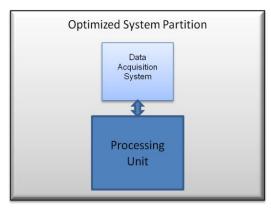

| Figure 93 Original System Partition Design                       | 110 |

| Figure 94 Optimized System Partition Design                      | 110 |

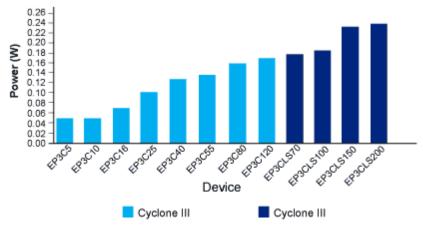

| Figure 95 Programmable Chip Power Consumption                    | 111 |

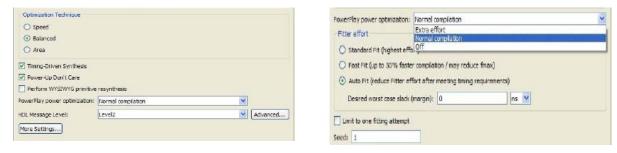

| Figure 96 Power Optimization Options                             | 111 |

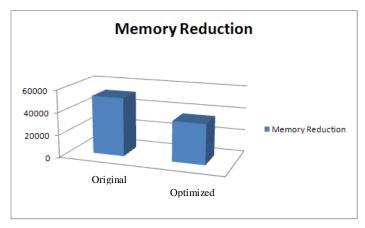

| Figure 97 Memory Resource Reduction Result                       | 120 |

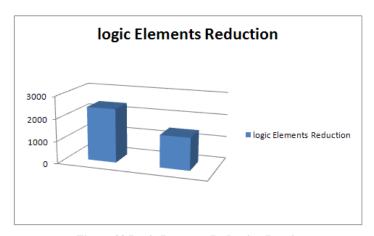

| Figure 98 Logic Resource Reduction Result                        | 120 |

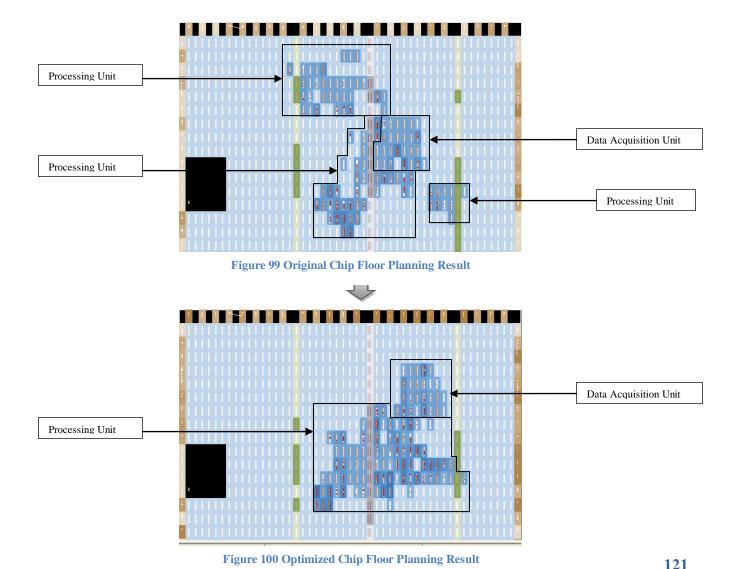

| Figure 99 Original Chip Floor Planning Result                    | 121 |

| Figure 100 Optimized Chip Floor Planning Result                  | 121 |

| Figure 101 More optical imaging coverage                         | 125 |

| Figure 102 More robust processing handling                       | 126 |

| Figure 103 SoC Design                                            | 126 |

| Figure 104 FPGA Chip                                             | 126 |

| Figure 105 Migrated ASIC Chip                                    | 126 |

## **List of Tables**

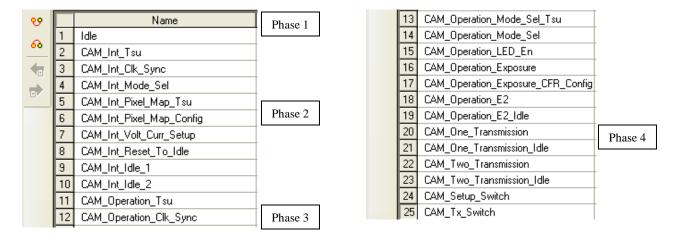

| Table 1 Acquisition Controller State transition Table                              | 31  |

|------------------------------------------------------------------------------------|-----|

| Table 2 ADC Interface State Transition Table                                       | 37  |

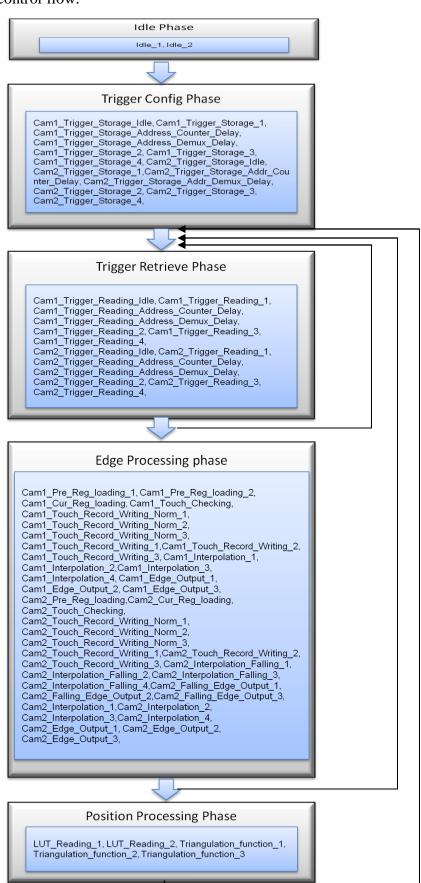

| Table 3 Master Controller State Transition Table                                   | 68  |

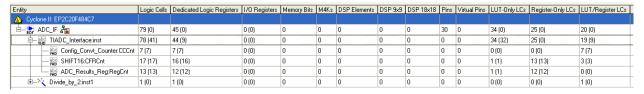

| Table 4 Original System Resource Analysis Table                                    | 113 |

| Table 5 Optimized Memory Resource Analysis Table                                   | 114 |

| Table 6 Gradient Based Edge Detection Algorithm Resource Analysis Table            | 115 |

| Table 7 Dynamic Linear Approximation Detection Algorithm Resource Analysis Table   | 115 |

| Table 8 Original Edge and Position Localization Units Resource Analysis Table      | 116 |

| Table 9 Optimized Edge and Position Localization Units Resource Analysis Table     | 116 |

| Table 10 Original Acquisition Controller and ADC Interface Resource Analysis Table | 117 |

| Table 11 Optimized Acquisition Engine Resource Analysis Table                      | 117 |

| Table 12 Optimized ADC Interface Resource Analysis Table                           | 117 |

| Table 13 Multiplexer Restructuring Results Table                                   | 118 |

| Table 14 Retiming and Register Balancing Results Table                             | 119 |

## **List of Abbreviations**

| Abbreviation | Meaning                                 |

|--------------|-----------------------------------------|

| ADC          | Analog-to-Digital Converter             |

| ALU          | Arithmetic Logic Unit                   |

| ASIC         | Application Specific Integrated Circuit |

| BBD          | Block Based Design                      |

| BSE          | Binary Search Engine                    |

| CPU          | Central Processing Unit                 |

| DAU          | Data Acquisition Unit                   |

| DCM          | Digital Clock Manager                   |

| DSP          | Digital Signal Processor                |

| EDU          | Edge Detection Unit                     |

| FPGA         | Field Programmable Gate Array           |

| GPU          | Graphics Processing Unit                |

| LED          | Light Emitting Diode                    |

| LUT          | Look up Table                           |

| MMU          | Memory Management Unit                  |

| PBD          | Platform Based Design                   |

| PC           | Personal Computer                       |

| PLU          | Position Localization Unit              |

| PU           | Processing Unit                         |

| RAM          | Random Access Memory                    |

| SAW          | Surface Acoustic Wave                   |

| SOC          | System on Chip                          |

| TOC          | Touch Screen on Chip                    |

| USB          | Universal Serial Bus                    |

## **Chapter 1 Background and Introduction**

## 1.1 Background and Requirements Analysis

#### Conventional Touch Screen Technologies

Touch screen technology has been developed as a popular interactive component in everyday life to facilitate human-to-machine communication and enrich user experience. There are conventionally four types of touch screen input devices based on different technologies. They have been applied to various applications with their own advantages and disadvantages where:

- Resistive based touch screen solution is relatively cost efficient and supports multiple input means (fingers, gloves, and stylus) but has the drawbacks of image clarity degradation in public environments and the requirement of periodic calibration.

- Capacitive based touch technology is considered durable and reliable when applied in harsh environments (water, dirt and dust) but has disadvantages in input methods capability (most are restricted to finger input) and scalability (the technical difficulty and high cost of applying to large formats).

- Surface Acoustic Wave (SAW) constructed touch device provides high quality image clarity and light transmission however with the same restriction in large scale capability and cost efficiency.

- Infrared oriented touch technology has the unique integration advantage of being a completely sealed in device, but is also regarded as having a relatively poor touch function performance and it is vulnerable to complex environments (contaminants etc).

#### Optical Imaging Based Touch Screen Technology

The optical imaging based touch screen solution has emerged in recent years as a new competitive technology which has its own distinct characteristics leading to a significant variety of advantages over the aforementioned traditional approaches.

In general, it is a compact and efficient image sensor and reflective retro combined solution designed to realize touch screen functionality with minimum cost and great scalability.

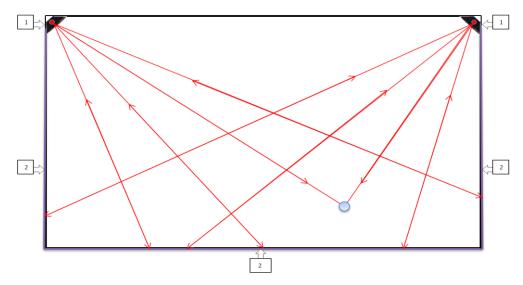

The simplified optical imaging based touch screen system is illustrated below in figure 1:

Figure 1 Simplified Optical Imaging Based Touch Screen System

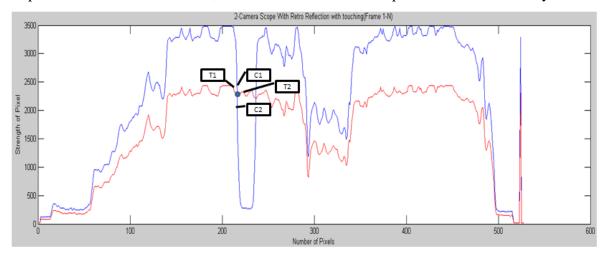

Inside the basic optical touch system, there are two image sensors (each being single line scan based, one at the left top corner and the other at the right top corner) with a LED positioned on top of each sensor chip (1). Specific reflective material has been placed along the screen edge (2). The simplified system mechanism is when there is no object within the active touch screen area all the infrared light emitted by the two LEDs will be reflected back to the image sensors by the retro material at the screen boundary; the image sensors receive the full level light reflection as below in figure 2:

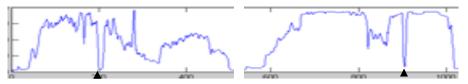

Figure 2 Left and Right Line Scan Sensors Waveform

When an object occurs within the touch screen active area, part of the reflection will be blocked as shown below in figure 3:

Figure 3 Left and Right Line Scan Sensors Waveform with Single Touch

By converting the blocked waveform locations to actual angles from the sensor view points, and coordinating with the physical screen dimensions, the actual touch point is able to be triangulated and its position calculated. Moreover, a significant number of advanced methods and techniques have been evolved based on the basic mechanism as described above to achieve real time high quality performance. The basic optical imaging control and process unit behind the system is comprised of a microcontroller which directs the timing sequence of the LED based illumination subsystem and image sensor subsystem to acquire and transmit the raw touch information. A PC based processing system abstracts the edges, localizes and finalizes the touch positions, resolves the occlusions etc. The existing system is relatively accurate, robust and meets the current real time requirements reasonably well. Nonetheless, a certain number of system limitations and additional requirements have been identified.

#### Requirements Analysis

With the ever growing market competition and increasing customer expectations, there are three new design requirements investigated in this research: Low level system acquisition requirement, high level processing requirement and system cost requirement on the resource level.

#### System acquisition requirement

The general-purpose microcontroller based data acquisition unit is a system bottleneck which relies on a sequential acquisition mechanism with a relatively limited frame rate. Customized acquisition control logic is urgently required, to execute a concurrent acquisition control structure where one image sensor is capturing image pixels while the other sensor is simultaneously digitizing and transmitting the pixels. The significant increase in the touch information frame rate is required for fast touch activity detection and touch history tracking, which will play an important role in the subsequent processing module.

Another major problem in the current optical imaging based system is the touch occlusion issue which is largely caused by lack of sufficient screen imaging information. Furthermore, a fundamental requirement of the next generation operating system is the supporting of multiple touches that demands more accurate coverage of screen information from more different camera view perspectives. Therefore, it is important that the proposed acquisition control logic is not only able to provide a more efficient concurrent mechanism for improving the frame rate but should also have the capability and extensibility for handling a larger camera based bandwidth in a more advanced system.

#### System processing requirement

In current touch screen systems, the majority of system processing functionality has been placed on the PC processor with a combined latency of sequential acquisition delay and PC algorithm operation time. With the potential increase in the number of acquisition sensors and frame rate, longer latency will occur in the current acquisition engine and more processing load will placed on the general-purpose CPU which is also shared by other applications within the OS. In order to reduce the low level system latency under the increasing data rate and computational pressure, it is necessary that certain processing in the critical path is pipelined and pre-processed with the acquisition process. Pre-processing operations such as edge detection, ambient subtraction and pre-touch indication leads to the process-on-the-fly requirement.

#### System resource requirement

Market and cost considerations are always involved in real product development. A minimum amount of hardware resources is demanded in this industrial research for realizing the aforementioned concurrent acquisition engine and pre-processing module. Moreover, a further interest has been expressed for this project to explore and analyze the feasibility and resource consumption of a complete on-chip hardware solution achieving basic touch screen functionality to lower the overall manufacturing cost.

## 1.2 Objective and Methodology

This is investigative research based on real world touch screen system requirements, which aims at creating customized logic to acquire touch information and further explore the feasibility of a complete on-chip hardware solution to realize basic touch screen functionality. There are three objectives in system research and development according to these requirements:

- Create a customized and more advanced data acquisition system compared with the existing platform in terms of its operation mechanism, speed, accuracy and noise level.

- Research and validate the concept of embedding a complete touch system on a chip with an incremental design and verification process.

- Optimize the resource utilization without compromising overall system performance.

For the system design methodology, it is necessary and critical to understand the existing system structure and functionality. Therefore the same functionality is required to be migrated to a new platform (a field programmable gate array) on the system level with the consideration of technology differences and the explicit partitioning of different system modules. After that, more sub-modules are designed, constructed, verified and tested to realize the required system level functionality with constrained timing requirements. Then all top level modules are integrated and synchronized to achieve system timing closure with a well organized control flow. In the end, a number of optimization techniques will be applied to both system level and module level components to minimize the resource consumption while maintaining the same functionality.

During the development process, there are three design phases:

Phase One: Data Acquisition System

Phase one is a performance oriented design process with the purpose of constructing a high speed, concurrent data acquisition engine to replace the existing general purpose microcontroller based acquisition system. It is planned to start by constructing the image sensor timing control logic with the basic capability of configuring and controlling sensors to acquire analog pixels, equipped with a LED based illumination subsystem with more complicated timing control between the shutter and operation modes. After that, an analog-to-digital convertor is added to

digitize the analog signals which will be further transmitted out of the data acquisition system through a USB module. Each module will operate at the highest possible execution speed by taking advantage of the pipeline structure. It is acceptable that extra resources are consumed to reduce overall noise level and a new concurrent timing control mechanism is expected to maximize system operation efficiency. The data acquisition system is aimed initially to achieve the highest possible system performance without consideration of resource consumption. At the end of phase one, a number of tests are required to verify the real time performance is acceptable.

#### Phase Two: Processing Unit

The development of the processing unit is considered as an investigation and verification process using the incremental design methodology [1] where each new module is constructed and then integrated with the previously verified system. The design objective of the processing unit is to realize basic touch screen functionality with minimum concern for resource use. Based on raw touch information collected by the Data Acquisition System, the Processing Unit design process starts from a proposed memory management unit to store and direct image frames before further processing. Dedicated logic blocks are required to perform initial edge detection, then touch position localization and initial touch level detection, then touch motion tracking. Each block development will go through its own verification and test process [2]. Finally, it is necessary to have a system master controller synchronizing and organizing all processing modules, to respond to both the acquisition system and PC through a customized transmission engine. A software interface is required to demonstrate the correct functionality of the basic touch screen system during real time user testing.

#### Phase Three: System Optimization

After successfully establishing the proposed touch screen system, a number of optimization techniques are applied to the acquisition system and the processing unit on different levels (from the algorithm level to the logic gate level) to minimize resource consumption without compromising overall system performance. An optimized on-chip hardware solution with proven real time performance will be validated as the result of this research.

## 1.3 System Abstraction and Overview

This research is based on real world touch screen application requirements with specific investigation, implementation, verification, validation and optimization involved to create a dedicated on-chip solution. Field Programmable Gate Array based application specific control logic is proposed and developed in this research not only to investigate the possibility of a customized acquisition engine with desirable performance but also to explore the feasibility and capability of an on-chip touch information processing unit with the minimum consumption of system resources. The abstraction layer of the system is illustrated below before being expanded and explained in detail in later chapters.

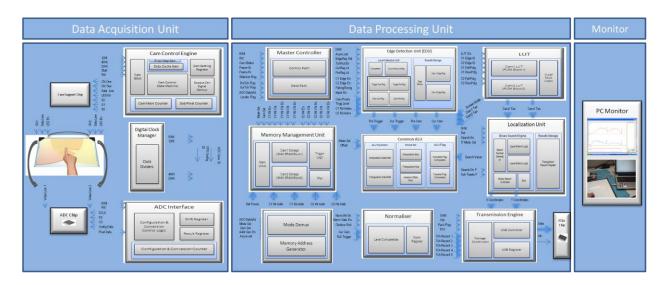

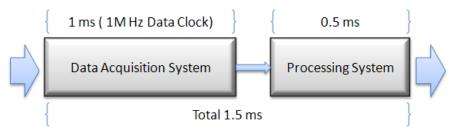

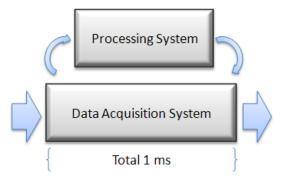

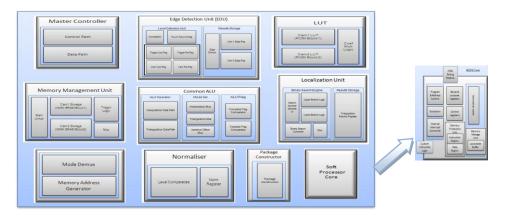

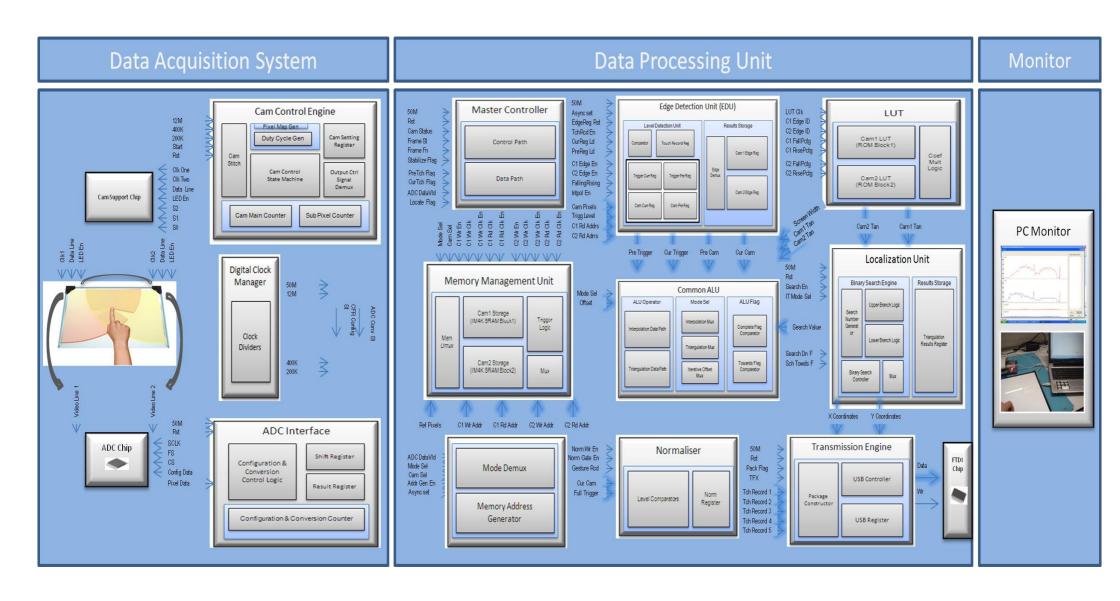

The complete system is comprised of three major modules: Data Acquisition Unit (DAU) which controls and coordinates the image sensor, illumination and ADC subsystems to consistently acquire, digitize and transmit the real time touch information to processing logic; Processing Unit (PU) which performs real time touch detection, object positioning and motion analyzing with low latency characteristics by taking advantage of a pipeline structure; and a PC monitor which continuously updates the touch screen optical imaging scope and user touch positions.

The following is the simplified system block diagram on an architectural level:

Figure 4 Simplified System Block Diagram

The following paragraphs will concisely introduce the design concept and system flow with an overview of how the system operates. Brief explanations of the main components integrated inside the three main blocks are presented here.

Inside this vision (image sensor) based real time touch screen system, the **Data Acquisition Unit** (DAU) plays a fundamental role in raw optical imaging information acquisition by controlling and organizing the **Line Scan Sensors**, **LED** based Illumination system, **Sensor Support Chip**, **ADC Chip**, **ADC Interface Logic** and **Digital Clock Manager** (DCM). The unit is designed and partitioned as a self-contained module with the **Data Acquisition Control Engine** operating all control signals within the unit so there is no interference with other units.

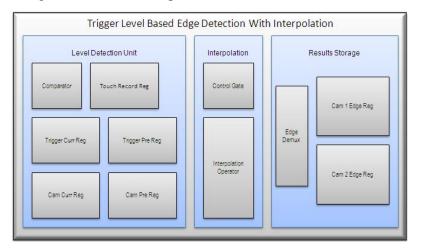

The **Processing Unit** is the key block of the whole touch screen system. The digitized image frames from the Data Acquisition Unit are redirected by **Mode Demux** to be either stored into **RAM** in the **Memory Management Unit** (MMU) in iunitialization mode or fed into the **Edge Detection Unit** (EDU) and **Normaliser** when in operation mode. The **Trigger Logic** inside the MMU adjusts the threshold level for different ambient light environments while the **Memory Address Generator** updates both the reading and writing addresses for the MMU. The Edge Detection Unit (EDU) is constituted of a **Level Detection Unit** which defines and indicates the touch action and the **EDU Result Register** which stores both the rising and falling edges of the touch for both image frames.

More accurate touch edge positions can be obtained using the **Interpolation Data Path** inside the **Common ALU** module catering for more precise requirements. All touch edges are translated from image Pixel Ids into real angles in the detection area from both the top cameras' perspectives, using a pre-calculated **Look up Table** (LUT) in ROM. After that, the two angles are triangulated in the **Position Localization Unit** to calculate the x and y coordinates of the touch on physical screen. The **Triangulation Data Path** is involved in localization processing while the hardware **Binary Search Engine** is used to optimize the search process by accelerating the system critical path to a significant extent.

The Normalizing Process inspects and analyses subtle application actions such as pre-touch using the **Level Comparator and Register** module inside the **Normaliser**. This runs in parallel with the Edge Detection and Localization. As a result, the most recent touch percentage levels will be stored in registers for further touch history tracking analysis. Finally, both the concurrent processed results (touch position and tracking history results) are reconstructed in packages by the **Package Constructor** in the **Transmission Engine** and transmitted outside the block.

The **Master Controller** inside the Processing Unit is the core element of the system operation which not only directs process flow and organizes control signals to and from sub-modules simultaneously, but also coordinates and interfaces with the Data Acquisition Unit and PC monitor to achieve real time system synchronization and coherence.

The **PC Monitor** receives data transmitted from the hardware touch screen system through a **USB2.0** connection. The software interface is designed for high speed USB transmission with two GUIs: one for displaying the raw touch screen optical imaging information for development debugging and data acquisition process validation; and the other for updating actual real time touch position results based on the hardware processing unit in a visual form for system demonstration purposes.

All units and modules abstractly aforementioned will be further discussed and illustrated in detail in the next few chapters.

## **Chapter 2 -- Literature Review**

### 2.1 Hardware Accelerated Hybrid System

In modern electronic system design, with increasing demands in processing capability and more stringent requirements for system latency, it is difficult for a real time application to fulfill design specifications if it is only implemented in software. The hardware accelerated hybrid system [3] emerged due to this reason in the early 1990s to describe a process where certain parts of the program's critical functions are constructed in hardware to meet performance target and timing constraints while other parts are implemented in software in the processor. It is informed by multiple design disciplines and approaches based on the characteristics of an application which can be classified as a software-oriented hybrid system, hardware-oriented hybrid system or software/hardware co-design system.

### 2.1.1 Software-Oriented Hybrid System

For software-oriented heterogeneous system design, without violating any application performance constraints, a significant proportion of system functionality has been implemented in software with a minimum amount of hardware processing. Most often, software-oriented design takes advantage of the existing processor or microprocessor structure (either general purpose or special purpose) with dedicated software programs that allow the user to define the desired functionality using a specialized language. On the instruction level, as indicated by [4], programming is achieved by executing on the hardware supported by the existing architecture. It is considered to be more flexible with a relatively high level of software and lower cost by implementing major system design into the available structure with very limited extra hardware cost. Compared with a pure software solution, the software-oriented hybrid system is more efficient with a hardware acceleration of a small part of the system.

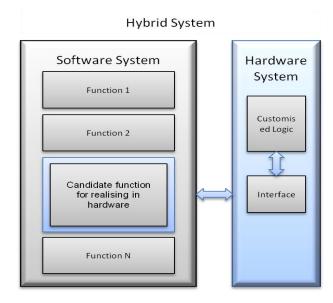

The software-oriented hybrid system structure is illustrated below redrawn from [3]:

Figure 5 Software-Oriented Hybrid System

#### Low Level Latency Requirements

In most software-oriented hybrid system design, the key processing timing and latency requirements are less demanding which makes it easy and cost-efficient to implement the major proportion of system functionality into general processor based software. For example, in Garufi and Acernese's hybrid modular control and acquisition system [5], with low sampling and performance requirements, the complete distributed control algorithm was processed by PC based software with low cost hardware logic used in the critical acquisition path. Another example is the control design for swing scanning infrared earth sensor application [6]. The entire earth wave algorithm has been executed in an embedded ARM processor with necessary acceleration in obtaining raw data by taking advantage of the hardware structure.

#### Flexibility and Extendibility

For some other software-oriented systems, the specification requires flexibility and adaptability because a certain amount of system functionality is to be executed unpredictably and sporadically. Thus, it is natural to implement the majority of the proposed design into a standard software core to allow rapid change to a new algorithm. The real-time dark environment vehicle detection system [7] is a good example. With basic hardware acceleration on pixel-level

operation, the main vehicle searching and decision making algorithm has been executed on processor based software because of the broad variety of possibilities and uncertainties.

#### Computational Cost and Execution Convenience

Sometimes the system functionality is technically difficult and computationally expensive to be implemented into pipelined hardware or the required function is already an existing component of a processor based system. For instance, floating-point arithmetic operations are a basic element inside numerous algorithms which are widely supported by existing instruction sets inside conversional PC or processor based systems. And for modern software-oriented platforms (physical or soft [8] on chip processor core based system) it is also commonly supported. Thus, from the cost perspective, some applications are best suited to processor based design. Meanwhile, software-oriented design is considered efficient and convenient in terms of implementation cycle and requirements for specialized human resources compared with a fully customized hardware design.

#### 2.1.2 Hardware-Oriented Hybrid System

The aforementioned software-oriented hybrid system design usually has a high speed clock frequency and relatively powerful sequential computation processing ability. However the hardware-oriented design is practically application-specific with the characteristic of inherent parallelism to meet stringent user requirements. Usually, the operational frequency in hardware dominated design is much slower than PC or processor based system but with a capability to provide better performance through paralleling more operations, minimizing memory access and optimizing critical paths.

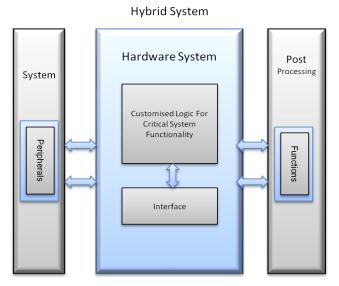

The hardware-oriented hybrid system structure is illustrated below: the majority of system functionality has been implemented in hardware logic with tight and multi-level interconnections between system peripherals and the subsequent processing block.

#### Hardware-oriented hybrid system structure:

Figure 6 Hardware-Oriented Hybrid System

#### High Throughput and Low Latency

In most high performance real-time applications, throughput and latency are two significant factors affecting the performance and outcome of the system. Morris, Thomas and Luk's [9] financial trading system is an example. "The combination of increased message rate and more complex market feed data format" naturally requires a system which has high bandwidth message processing capability and desired latency in a situation where large bursts of trading activity occurs. Software-oriented solutions are often unable to keep up with the input data rate and also have difficulty meeting the latency requirements of sub-millisecond response times. Under such circumstances, there is a shift during the application design towards a more hardware-oriented system with an accelerated propagation structure.

#### Functionality Effectiveness, Compactness and Robustness

With an explicit design specification or clear problem definition, the architecture of a hardwareoriented system is often constructed in a compact and application-specific manner such as [10] compared with a general processor software solution. In detail, the hardware dominated solution usually starts with a straightforward design approach which resolves the problem in a direct way that leads to better efficiency. The hardware oriented structure is usually more tightly interconnected and integrated with target requirements, which leads to a better solution because the hardware solution is more convenient for adding concurrent features inside each block and it is more versatile because it is more easily extensible.

#### Architecture Parallelism and Reduced Response Time

In safety-critical areas, such as medical instruments, the efficiency and efficacy of equipment design plays a crucial role in accurate and appropriate problem identification and localization, which sometimes reduces the instrumentation operation and response time, helping minimize unintended damage (such as to healthy tissue etc). Minimally invasive image-guided intervention (IGIs) is a typical application that benefits from the hardware-oriented design method with a significant improvement in execution time from hours to a few minutes compared with the conventional open and invasive procedure. Inside the IGIs workflow, the deformable image registration is the fundamental and major step, which in Dandekar and Shekhar's system [11] has been implemented into a highly pipelined multimodal based hardware architecture to reduce the procedure time.

In order to maintain the high level calculation accuracy, which is equally important in hardware occupied medical instrument design to minimize the possibility of complications, there are commonly two execution alternatives. One is constructing a dedicated floating processor unit at a high cost of hardware resources, such as plane-sphere intersection in a hardware ray tracing system [12] having an independent pipeline arithmetic unit for meeting accuracy requirements. The other alternative often used is the adoption of multiple look up table (LUT) based polynomial approximation. In Castro-Pareja, Jagadeesh and Shekhar's system [13], two LUTs (Interpolation Weights and corresponding floating coordinates) have been utilized to replace a standard arithmetic unit while achieving the same operational precision.

#### Security and Adaptability

For certain areas, such as military communications, there is a growing concern not only in traffic speed and bandwidth, but also in network security where a device is required to protect the intellectual property of a design from attempts to reverse engineer or replicate operation. The general-purpose processor based software solution is considered relatively unsecure in terms of concealing internal algorithms since "their reliance on external instruction streams means that they are susceptible to instruction bus monitoring attacks while operational" [14]. In order to maintain network security, hardware based solutions are used where the critical function has been separated and implemented into hard-wired logic in a self-contained manner without requiring external instruction data. At the same time, by taking advantage of the capability of run-time reconfiguration of certain hardware devices, new protocols and algorithms are able to be processed and adopted without compromising performance. The information exchange security system based on specialized hardware has demonstrated a more capable security monitoring mechanism and in addition the "reconfigurability and expandability of the solution provides an apparatus for further improvement and elimination of potential threats that are still to arise" [15].

#### 2.1.3 Hardware/Software Co-Design System

The hybrid hardware/software co-design [16] emerged to embrace new design requirements in the early 1990s to describe a process where part of the program's functions are constructed in hardware while the others are implemented in software in a processor. The increasing use of the co-design method for complex systems stems from a variety of factors. One is "the need for multi-formalism specification" [17] where most modern embedded systems consist of different components (analog, digital etc.) and there is no common description or language to cope with specification variations within the system. Another is the market pressure for real-time products which demands shorter development cycles and effective design cost. Last but not least, design reuse is a key issue in complex system design convenience and coherence.

The hardware/software co-design is the net result of a significant number of research activities in the embedded area. It is informed by multiple disciplines including software/hardware partition design, application-oriented hardware circuits design and hardware/software domain interface design. Compared with the aforementioned hardware-oriented design and software-oriented design, there is neither an explicit overall performance constraint demanding a complete hardware solution nor a pure software solution fully satisfying the specification without acceleration.

#### Hardware/Software Co-Design Approach:

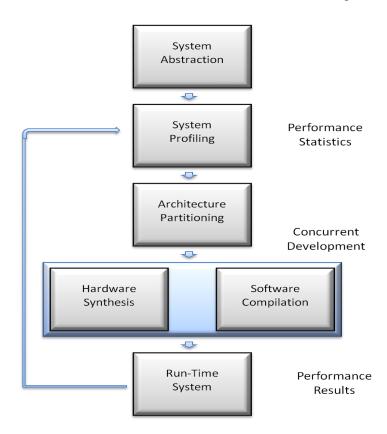

There are a number of fundamental stages for establishing a complex system following the codesign approach: from system specification, system profiling, architecture partitioning, concurrent hardware and software development to the actual run-time system. The general approach route is illustrated below redrawn from [18] with minor changes:

Figure 7 Hardware Software Co-design Approach

#### **System Abstraction**

The abstraction of system functionality based on heterogeneous specifications can also be described as "modeling system functionality and constraints" [18]. It is usually considered as a high level behavioral description regardless of implementation details.

#### System Profiling

System profiling refers to the identification of performance in critical regions and the timing estimation for real time operation using software (for instance C code) without real execution on the candidate architecture.

#### **Architecture Partitioning**

Hardware/Software partitioning aims to determine which parts of the system should be implemented in hardware and which in software by applying various trade-offs and spectrums [19]. As further explained by Ismail and Jerraya [20] the architecture is partitioned by assigning the whole system functionality to concrete parts of the physical system, which will be either compiled into machine code in a processor or synthesized into a hardware circuit description. The final system architecture formalizes the result of "several successive trial and error iterations of this step" [17] based on the detailed specification, timing constraints and designer's experience.

#### Concurrent Development

During the implementation stage, the hardware compilation and software compilation are executed simultaneously after the system evaluation and partitioning from previous stages. The concurrent development follows different design processes where hardware compilation is composed of hardware behavior description, optimization, synthesis, placing and routing, linking etc using a modern reconfigurable platform while software compilation generates machine code for the processor structure.

#### Run-Time System

The run-time system is the final operation platform which varies according to applications, such as a general-purpose CPU with Field Programmable Gate Array, or an application-specific processor with an application-specific-integrated-circuit.

To conclude, In order to achieve hardware/software co-design success, it is not only critical that the initial partitioning be made appropriately into hardware and software, but also that the ensuing system level development proceeds along lines that benefit from an integration of both hardware and software perspectives. Compared with traditional design, it is more efficient to plan the design with a more detailed specification available before selecting the final architecture. It is less costly to modify parts of the system between different partitions at later stages of development and it is easier to facilitate the final integration between different technology domains. Alternative system implementations are considered with respect to performance, physical aspects, reliability, modifiability, maintainability and manufacturing cost as emphasized by Purvis and Franke [21].

## 2.2 Image Acquisition and Processing

Vision based systems have been a popular research topic for the last decade where a significant number of areas have benefited directly or indirectly from it, such as robotics and autonomous systems [22], surveillance [23] and navigation systems [24]. It is also considered to be the general research and knowledge background for the proposed touch screen system. Vision systems aim at enhancing and improving the visual image characteristics for a human viewer through a variety of techniques and processes depending on applications. The acquisition capability which refers to large volume data handling, memory bandwidth and real-time constraints [25] and the processing ability which depends on the efficiency and parallelism of algorithms, arithmetic and logic operations are two major factors that determine the success of a vision based system.

There are three critical stages during the vision system design which includes data acquisition, system pre-processing and high-level processing.

#### Image Acquisition

Inside a vision based system, data acquisition is the fundamental image-sensor based integration control and read-out process to "set the mode of operation, address the pixels and transfer the data to high-speed local storage" [26]. And the difficulty of designing such an acquisition system usually lies on the efficiency of the interface which is the bridge connecting the system's front end and back end processing [27]. Usually, the image acquisition storage structure is developed by consideration of the related processing unit which has an impact on data collection.

#### System Pre-Processing

In recent real-time application development, there is an increasing trend towards the system preprocessing unit design because of the pressure of larger volume data from multi-inputs and the stringent performance and latency requirements. In the image processing area, the pre-processing is usually referred to three major components: image enhancement, feature extraction and interest segmentation. **Image enhancement** is a basic restoration approach to make subsequent analysis easier over environmental variation [25] through a number of techniques such as noise reduction, contrast or color correction [28] and lens distortion. The second important component in image pre-processing is **feature extraction** where typical properties like lines, edges [29], texture and shapes [30] can be extracted to reduce raw data size in order to reduce the processing burden on the main system. Last but not least, the interest segmentation step refers to "the selection of a specific set of points or regions of interest which are the subject for further processing" [31]. On the pixel level, the image segmentation task functions on the spatial domain "grouping together neighboured pixels or voxels to homogeneous regions if they can be considered to be similar according to a common feature" [32]. In general, the purpose of preprocessing is to robustly abstract typical characteristics and information useful for subsequent processing from the image to further optimize overall system processing distribution.

### **High-Level Processing**

High-level processing is the critical stage of collecting, analyzing and generating the final system outputs. The results after advanced processing are likely to be route and movement decisions from a vision based navigation system [24], or the identification of a person from a face authentication system [33]. The high-level processing is usually performed by a general or

specific processor structure because of the variety, flexibility and complexity of the dedicated algorithms.

On the implementation level, a number of studies have investigated the optimum system structure partitioning between hardware and software in different applications.

In two dimensional image based vision detection, Alt, Claus and Stechele [7] have built a vehicle detection system where the image acquisition, spotlight detection and region labelling are partitioned in a hardware structure while light pair searching and plate searching are executed in an embedded processor. Pei, Chun and Li [34] have a similar design partition in their departure warning system with frame acquisition and liquid-crystal display and other peripherals controlled by hardware. The implementation of a fundamental Gaussian smoothing filter based global edge detector has been proposed in hardware from their research. In order to meet increasing system performance requirements in real time, more and more researches have shifted intensive image processing units from software-executed processors and customised this into more applicationspecific logic structures. For example, Bonato, Marques and Constantinides [35] describe a feature detection system, in which major system processing such as pixel streaming, magnitude calculation, orientation computing, and key points detection and classifying are constructed in logic structures and the embedded processor is used to generate descriptors for future feature extension. Vicente and Munoz [36] describe an object counting and tracking system which is constituted of critical object and contour detection algorithms constructed in hardware structures and more flexible classifying and tracking modules implemented in a processor.

Furthermore, in other performance-oriented research applications, more hardware resources are consumed to achieve design goals. For example, Ishii, Taniguchi and Yamamoto [37] have developed a high speed (1000fps) real time vision platform where most image processing algorithms (multi-target colour tracking, feature point tracking, optical flow detection, and pattern recognition) are accelerated by a hardware pipeline structure. Another example is Yean and Yu's [38] Smart Camera system for Gesture Recognition in HCI Applications The complete Harris keypoint detection algorithm and Kanade-Lucas-Tomasi (KLT) feature tracker algorithm have been implemented in a logic structure.

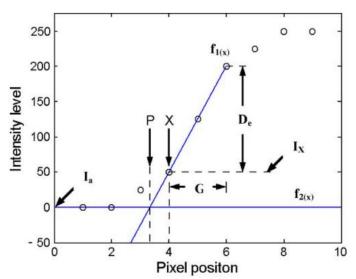

The proposed touch screen system is a **line scan image sensor based specific object detecting** application. Ohtani, Baba and Notohara [39] have built an optical measurement system with the analogue scan unit and ADC conversion controlled by software in a processor while hardware is responsible for actual spot position calculation from digitized information. In Hussmann and Ho's real-time edge detecting system [40], hardware was used for most elements inside the system including sensor scan circuits, ADC conversion, and low-pass filter. In addition, a simple edge localization algorithm was constructed in hardware. The processor was used for further advanced post-processing. From their work, it is suggested that the fundamental architectural, data-path critical and computationally less complex functions are more efficiently implemented in hardware while software is preferred to handle more flexible features. These design considerations will be applied in constructing the touch screen system.

### 2.3 Field Programmable Gate Arrays

Field Programmable Gate Arrays (FPGAs) are reprogrammable hardware devices that can be utilized to implement logical functions through a hierarchy of reconfigurable interconnects among digital blocks. It is the advanced technology having both the execution speed by taking advantage of the parallel hardware architecture and the implementation flexibility through the programming approach. In modern designs, there is a growing trend in applying FPGAs as development and product platforms. There are three major types of FPGAs among different vendors: SRAM based FPGA, Flash based FPGA and Anti-Fuse based FPGA[41].

#### **SRAM FPGA**

Static memory technology based Field Programmable Gate Arrays are widely used by major vendors such as Altera and Xilinx where power is required to be sustained to retain the internal data during the operation. Usually an external boot device is needed to provide in-system programming through bit streams.

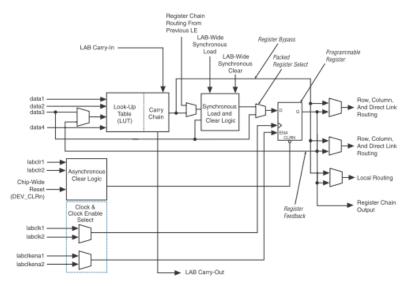

The following is the basic logic element structure from an SRAM based Altera Cyclone II device [42]:

**Figure 8 SRAM Based Logic Element Structure**

The basic logic element is composed of a four-input look-up table (LUT), which is a function generator that can execute any function of four variables: a programmable register which can be configured as different logical operations such as D flip flop or T flip flop; a carry chain for function directing; a register chain for unit cascading; and some other components for controlling and linking signals.

#### Flash based FPGA:

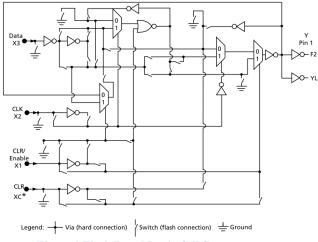

Flash-erase EPROM based Field Programmable Gate Arrays are reprogrammable and low-cost hardware devices. The FLASH based FPGA is able to retain the value after power-off and will always leave residual charges after being erased.

The following is the logic cell of a Flash based Actel ProASIC FPGA device[43]:

Figure 9 Flash Based Logic Cell Structure

The basic cell structure also has a look-up-table (which is a common component in most FPGA devices) with three inputs that can implement a three-input combinatorial gate or flip-flop with enable. This flash based Actel device is similar to basic ASIC cells in the sense of its fine granularity.

#### Anti-Fuse based FPGA

Anti-Fuse based Field Programmable Gate Arrays are less used due to their limitation of onetime programmability. However, its less flexible physical structure has relatively high security that prevents illegal etching and design retrieving.

#### FPGA Verses ASIC

After establishing a proposed hybrid system with proper considerations on system level partitioning and module level integration, it is usually required to convert all or part of the system into an application specific design (ASIC) to lower product cost and increase system reliability, especially in high volume applications. The ASIC design process and semiconductor process performance characteristics vary according to different manufacturers. The efficiency of resource consumption is normally measured as the number of standard cells. Compared with the traditional ASIC design process which usually has a long design cycle and relatively high NRC (Nor-Recurring Cost), recently there is a growing trend to create hardware embedded simulations

to facilitate incremental design verification of ASICs by using FPGA (Field Programmable Gate Array) devices. With its high flexibility and short time-to-market, as indicated by Selvaraj, Sapiecha and Dhavlikar [44], this FPGA emulation has emerged as a major ASIC verification technology.

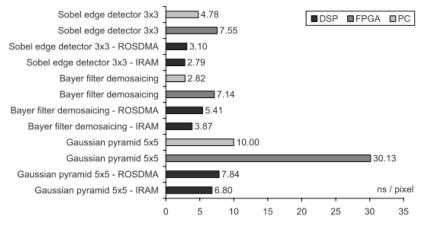

#### FPGA Verses DSP and Mobile PC

Compared with a Digital Signal Processor (specialized microprocessor for signal processing) and a Mobile PC (general purpose processing unit), parallelism is the most significant advantage in an FPGA which enables Process-On-The-Fly (processing during data acquisition), multiple operations within one cycle and multiple algorithms processed in a pipeline. The drawback is the relatively slow operational clock, relatively more expensive cost and much higher design and verification effort compared with an equivalent implementation running on a DSP or PC [31]. Powerful arithmetic operation processing capability is one well known feature of Digital Signal Processors, such as multiply accumulate (MACs) which is ideal for mathematical algorithms. Recent DSP's supporting of SIMD [45] (single instruction multiple data) featuring the instruction-level-parallelism through very long instruction words (VLIW) improves execution time to a great extent. The general processor is renowned for its super fast clock speed and multithreading for potential multi-cores. The following figure shows the results of a performance benchmark of selected vision based algorithms implemented on different high-speed embedded platforms: Field-Programmable-Gate Array (FPGA) (Altera Stratix- II families with 133MHz core), digital signal processor (DSP) (Texas Instruments TMS320C6414 with 1GHz system clock) as well as mobile PC processor (Intel Mobile Core 2 Duo T7200 with 2GHz clock) [31]:

Figure 10 Performance Benchmark of Vision Based Algorithms on Different Platforms

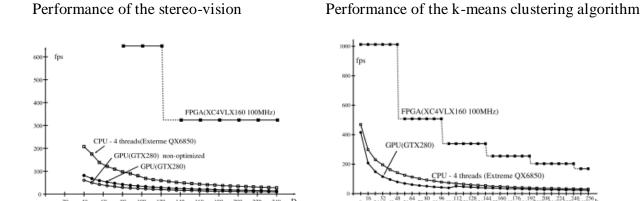

#### FPGA Verses GPU and CPU

FPGAs have shown very high performance in many applications in image processing. However, recent GPUs and CPUs also have the potential for high performance for similar applications. A Graphics Processing Unit (GPU) is designed particularly for intense graphic processing which usually has a much faster clock than a FPGA and a little slower clock than a CPU, but supports a significant number of cores (for instance, 240 cores in Nvidia GTX280) running in parallel and outperforms a CPU. The disadvantage of the GPU is the relatively slow memory access speed which affects the efficiency of communication and the limited data transfer between grouped cores fixed by its structure [46]. The following figure shows the relative performance for stereovision and k-means clustering algorithm. As computational complexity increases the performance of all GPU, FPGA and CPU based solutions decreases. However, the FPGA based design consistently outperforms both GPU and CPU solutions with the stepwise curve [46].

Figure 11 Stereo-vision and K-means Clustering Algorithms on Different Platforms

# 2.4 System on Chip (SoC)

With the rapid advance of electronic design automation and IC fabrication technology, System-On-Chip (SOC) has become more and more popular in complex system design which integrates data acquisition, signal conversion, application specific processing and various peripherals into a single chip. It refers to integrating all system components into a single circuit or chip to reduce manufacture cost and enable more compact systems.

Compared with traditional board level design, the System-On-Chip approach has a number of advantages in terms of higher system integrity, higher operation speed, lower development cost, more compact chip size and diminishing time to market. A typical SoC device can be a hybrid module with embedded processors, on-chip memory, versatile general purpose IO ports, high speed serial links, standard peripherals and other digital or analogue components[47]. In practice, external memory chips and various specific peripherals are often needed for different application requirements. The purpose of System-on-Chip development is to realize the required system functionality through a single chip resource with minimum external peripherals.

There are two main SoC development methods: **Block Based Design** (BBD) method and **Platform Based Design** (PBD) approach. For block based SOC design, the system is constructed based on assembling and coordinating a number of hardware blocks under subsystem functionalities to achieve an overall performance, while for platform based design, the system is a device integrating a predetermined collection of resources with a more system and model level focus [48]. Extensive research has explored methodologies and techniques on both design methods to improve the SOC design overall efficiency. Carloni and Li [49] proposed a latency-insensitive design (LID) to increase global performance in Block-Based Design. In the platform based approach, the reuse of intellectual property [50] and pre-designed blocks or virtual components (VC) [51] have been applied to boost design productivity.

A number of performance criteria have been required from modern industry system applications according to [52]. These are the demand for high-level integration and density of the target for the control module; the capability of supporting high-performance control algorithms with flexibility and modifiability; and "reliability, accuracy, and safety in a harsh environment". In order to meet most of the above criteria, recent research studies show that the digital hardware solution, such as the field-programmable gate array (FPGA), is an appropriate SoC development and implementation platform compared with other solutions.

The proposed touch screen system is an image sensor based design, using a Field Programmable Gate Array as a fast and advanced prototyping and implementation platform. In the image sensor based field-programmable-gate-array-executed detection and tracing system on chip area, within

the platform based design domain, Kim, Park and Lee's outdoor scene tracking system[53] has been designed relying on a platform based approach with a large amount of component reuse, such as the image encoder. Eun Tack and Kwang Sung have demonstrated an object and distance tracking SoC system based on field programmable gate array prototyping [54]. The on-chip system is comprised of processor core (ARM core), I2C control, SRAM control for stereo image capturing, DMA control, LCD driver and other basic peripherals. The distance and object tracking algorithm has been partitioned in processor based software. The development is under the guidance of the platform based approach where a variety of IPs have been adopted from previous designs such as LCD control IP and SRAM accessing IP. Moreover, the system has been further organized as a new IP for future platform development purposes.

Since the proposed research aims at providing a system solution for a specific application in a unique technology domain, it is estimated that most system functions and components are required to be constructed and customized according to specific application requirements and are unlikely to be reused as IPs in other designs. Therefore, block based design (BBD) is considered the most appropriate approach to initiate the design. A block based face detection system[55] is an appropriate example where the development process has been organized in three phases from a pre-processing block, detection block to post-processing block design. All key components have been constructed and verified on the module level, such as the Haar feature generator and ANN classifier, before being integrated incrementally into the whole system. A PowerPC based processor was used for memory control and future extension.

The System on Chip design is still a relatively new research field for system development in terms of high level system partitioning, design methodology and specific hardware level requirements. The design varies significantly according to different applications and knowledge of both architecture design and module verification is critical for achieving an optimum result.

# Chapter 3 -- Touch Screen System on Chip Design and Implementation

#### 3.1 Introduction

The proposed touch screen system was originally specified to perform two major system functionalities, acquiring touch information and processing touch results, with a number of submodules specified by the industry partner, such as an image sensor module and illumination support chip. A number of other sub-units were considered to be investigative, such as most of the blocks in the processing part of the system. Therefore, the traditional block based system on chip design method has been applied to the construction process with each module researched, implemented and tested separately and integrated incrementally as a complete system in the end.

The system has been partitioned into three main parts defined by the functionality on the top level:

- A Data Acquisition System which is designed to configure and control acquisition submodules to consistently collect and update touch screen based vision data.

- A Processing Unit which is designed to calculate and analyse the object position and touch motions based on the previous acquisition result.

- A PC module which is planned to handle and update touch positioning and motion results from the hardware block with data then passed to shared memory for future extension.

Each sub-module inside the acquisition and processing systems is dedicated to implementing one function. In addition there is a customized Acquisition Controller organizing all sub-units in the Data Acquisition System and a Master Controller coordinating all sub-modules in the Processing Unit for system synchronization. More details are presented in following paragraphs.

# 3.2 Data Acquisition System

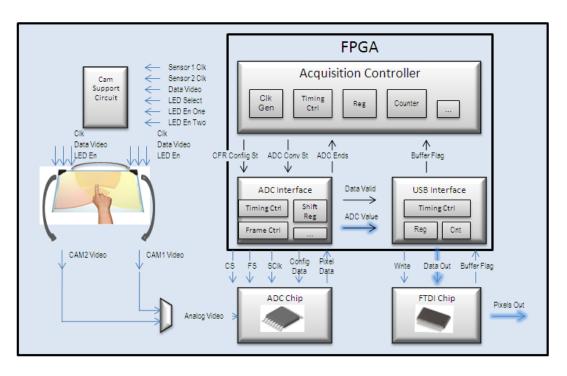

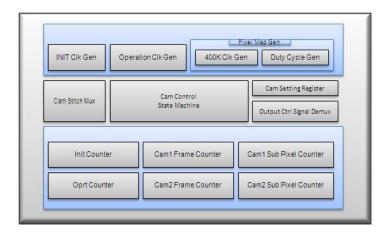

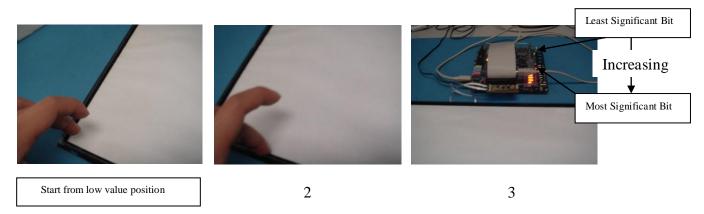

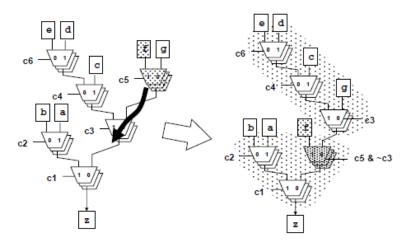

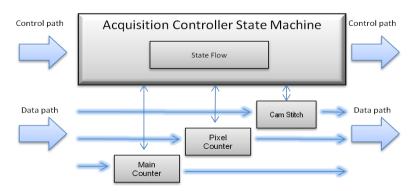

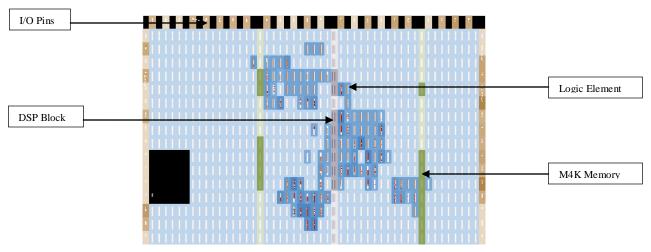

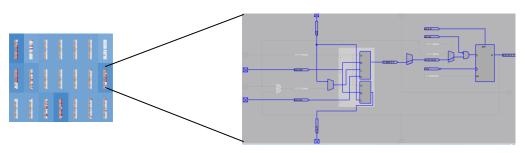

# 3.2.1 Data Acquisition System Overview