# Advanced Analysis of Supercapacitor-Assisted Low-Dropout (SCALDO) Regulator

## Kahambiliyawaththa Subasinghage Kasun Weranga

School of Engineering, Computer and Mathematical Sciences

Auckland University of Technology

A thesis submitted to Auckland University of Technology in fulfilment of the requirement for the degree of

Doctor of Philosophy

#### **Abstract**

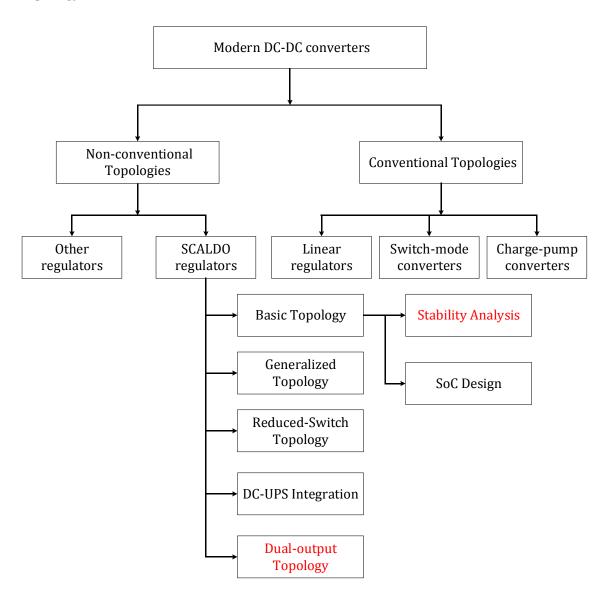

DC-DC converters can be found in three basic forms which are the linear regulators, the switch-mode power supplies (SMPSs) and the charge pumps. The combinations of these topologies are prevalent in power management circuits where the designers try to achieve cost-effectiveness, low output noise, high end-to-end efficiency and predictable transient response in these converters to make them suitable for a steady and constant power supply with regulation and multiple outputs.

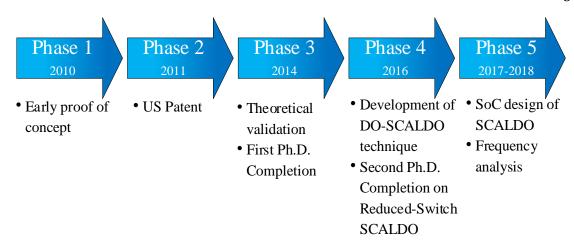

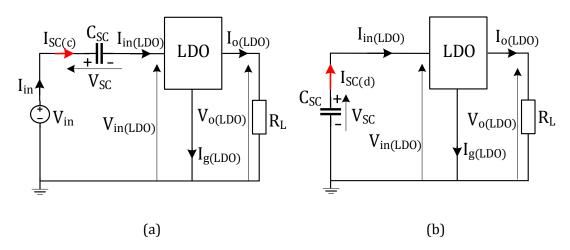

Combining an array of low equivalent series resistance (ESR) supercapacitors (SCs) and a linear low-dropout (LDO) regulator, a unique DC-DC converter topology has been developed over the past nine years; this technique is called the supercapacitor-assisted low-dropout (SCALDO) regulator. In the SCALDO approach, one or more supercapacitors are used in the series path of a LDO regulator as a lossless dropper and the excess energy accumulated in the SCs is recirculated at a very low frequency to increase the end-to-end efficiency by a multiplication factor in the range of 1.33 to 3. During the past several years, the SCALDO technique was further developed into many applications by introducing the reduced-switch topology and DC-UPS capability. Also, this technique has been identified as a potential area where further research can be carried out to match various power management requirements.

After a comprehensive investigation of feasible SCALDO implementation scenarios for multiple outputs, it was found possible to narrow them down to a detailed analysis of two output stages in a single converter which is substantial research for a PhD thesis. This dual-output converter is called the dual-output SCALDO (DO-SCALDO) regulator. In this method, dual-polarity voltage levels are generated from a single input voltage source whilst maintaining the useful characteristics of the original SCALDO approach such as high efficiency, low noise, fast dynamic response and low EMI/RFI issues. This thesis describes the conceptual background of the DO-SCALDO technique together with the working principles related to the different modes of operation. The theoretical concept is validated by the experimental results of a prototype version of a 12 V to ±5 V DO-SCALDO regulator. The steady-state and transient responses are investigated. The end-to-end efficiencies and the losses are

also determined, and the unique characteristics and potential advantages are compared with the commercial dual-output DC-DC converters.

In addition to the DO-SCALDO concept, the stability analysis of the single-stage SCALDO regulator is also considered as another potential area for further research. Since the SCALDO approach works based on a low-frequency SC circulation technique at the front end of a LDO regulator, the stability of the LDO regulator might be affected due to this external SC circulation network. Therefore, the overall circuit should be analysed for stability. The outcomes of this study can be used to stabilise the discrete SCALDO regulators or SoC (System on a Chip) designs. This thesis explores the design parameters and constraints regarding the stability of the fundamental SCALDO topology with the aid of the small-signal model. The open-loop transfer function is derived, and the possible frequency compensation techniques are identified. The theoretical small-signal model is validated from the simulated and experimental results of a 12 V to 5 V discrete SCALDO regulator, and the conclusions are made accordingly.

## **Table of Contents**

| Abstrac    | ct             |                                                                 | i     |

|------------|----------------|-----------------------------------------------------------------|-------|

| Table o    | f Cor          | ntents                                                          | iii   |

| List of l  | Figur          | es                                                              | vi    |

| List of '  | Γable          | 2S                                                              | ix    |

| Attesta    | tion           | of Authorship                                                   | X     |

| Acknov     | vledg          | gements                                                         | xi    |

| Nomen      | clatu          | re                                                              | xii   |

| Chapte     | r 1 Iı         | ntroduction                                                     | 1     |

| 1.1        |                | ckground                                                        |       |

| 1.2        | Res            | search objectives                                               | 4     |

| 1.3        | The            | esis outline                                                    | 5     |

| 1.4        | Pul            | olications                                                      | 6     |

| Chapte     | r 2 <b>L</b>   | iterature Review and Research Design                            | 7     |

| 2.1        | Int            | roduction                                                       | 7     |

| 2.2        | Op             | erating principle of the basic SCALDO regulator                 | 7     |

| 2.3        | Ger            | neralised SCALDO topology establishment and further advancem    | ent11 |

| 2.4        |                | pological differences of the SCALDO technique and switched-capa |       |

| 2 5        |                | iverters                                                        |       |

| 2.5<br>2.6 |                | ses in a SCALDO regulatorsearch Gaps                            |       |

| 2.7        |                | or art of conventional inductor-less split-rail topologies      |       |

| 2.7        |                | Buffer circuits                                                 |       |

| 2.7        |                | Switched-capacitor split-rail circuit                           |       |

|            | 7.3            | Limitations of conventional split-rail design topologies        |       |

| 2.8        | Res            | search design                                                   |       |

| 2.8        |                | Research questions                                              |       |

| 2.8        | 3.2            | Research scope                                                  | 22    |

| 2.8        | 3.3            | Research methodology                                            | 22    |

| Chapte     | r 3 <b>S</b> 1 | tability Analysis of the SCALDO Regulator                       | 24    |

| 3.1        | Int            | roduction                                                       | 24    |

| 3.2        | The            | e basic circuit diagram of the discrete SCALDO regulator        | 24    |

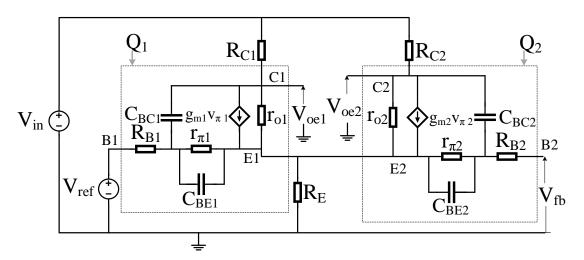

| 3.3        | Sm             | all-signal analysis of the basic SCALDO regulator               | 25    |

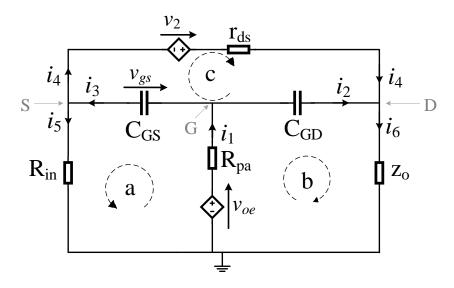

| 3.3        | 3.1            | Modelling of the pass device                                    | 25    |

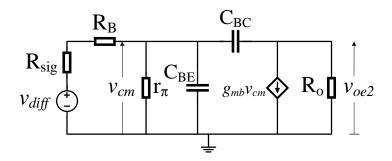

| 3.3        | 3.2            | Modelling of the error amplifier                                |       |

| 3.3        |                | Modelling of the SCALDO converter                               |       |

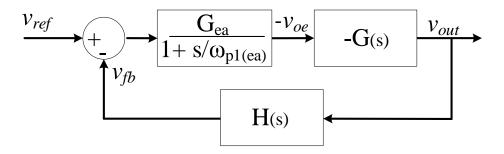

| 3.4        |                | e open-loop gain transfer function                              |       |

| 3.5        |                | tage control loop                                               |       |

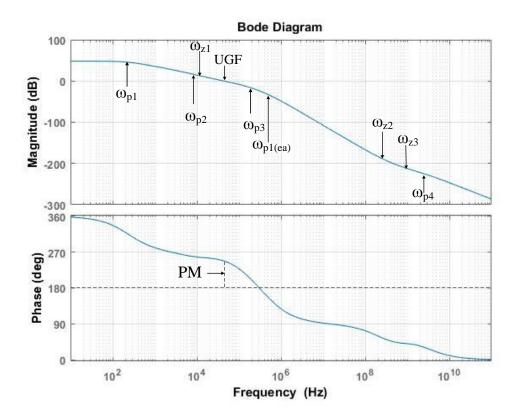

| 3.6        | Kel            | ative locations of the poles and zeros of the SCALDO regulator  | 38    |

| 3.7    |               | nparison of pole-zero frequencies of the LDO and the SCALDO regu                                |        |

|--------|---------------|-------------------------------------------------------------------------------------------------|--------|

| 3.8    |               | equency compensation of the SCALDO regulator                                                    |        |

| 3.     | .8.1          | Compensation using the output capacitor ESR                                                     |        |

| 3.     | .8.2          | Feedforward compensation                                                                        | 42     |

| 3.9    | Di            | scussion                                                                                        | 44     |

| Chapte | er 4 <b>F</b> | Experimental Validation of the Stability of the SCALDO Regula                                   | tor 45 |

| 4.1    | Int           | troduction                                                                                      | 45     |

| 4.2    | Di            | screte SCALDO design parameters                                                                 | 45     |

| 4.     | .2.1          | LDO regulator                                                                                   | 45     |

| 4.     | .2.2          | Supercapacitor switching controller                                                             | 47     |

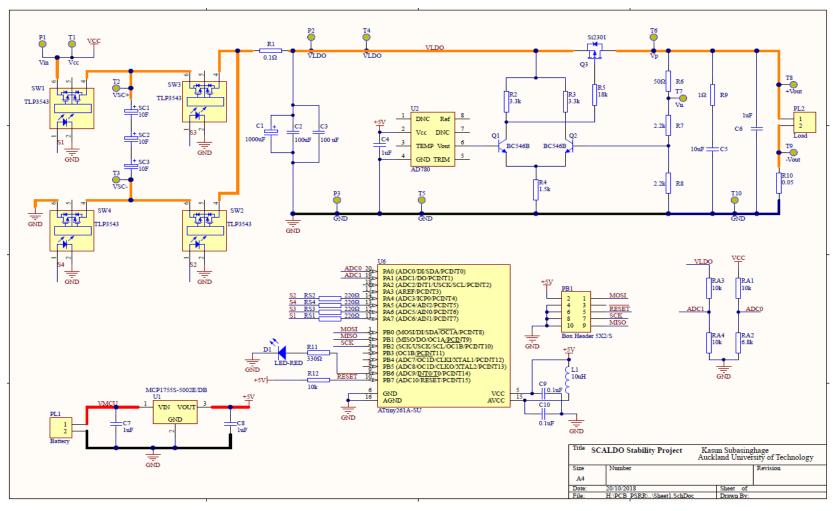

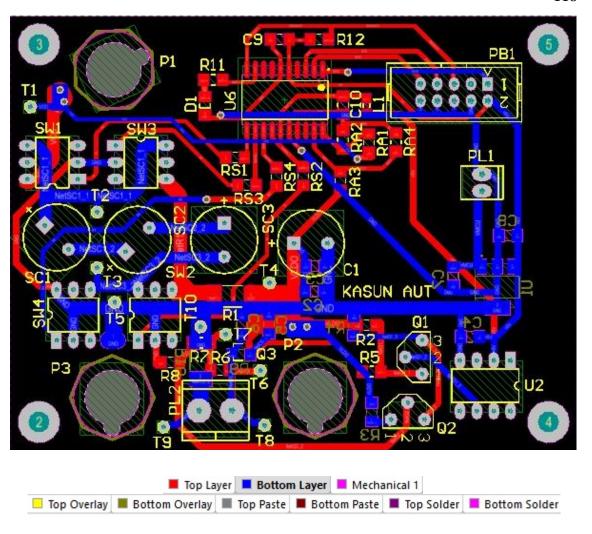

| 4.     | .2.3          | Circuit design                                                                                  | 47     |

| 4.3    | Th            | eoretical calculations                                                                          | 49     |

| 4.     | .3.1          | Determination of the stable range of the output capacitor ESR                                   | 49     |

| 4.     | .3.2          | Gain and phase calculation                                                                      | 50     |

| 4.     | .3.3          | Calculation of pole-zero frequencies against the equivalent resis of the switching network      |        |

| 4.     | .3.4          | Worst-case analysis to determine the circuit behaviour against t variation of design parameters |        |

| 4.4    | Sir           | nulation framework                                                                              | 56     |

| 4.     | .4.1          | Simulated open-loop response                                                                    | 59     |

| 4.     | .4.2          | Simulated pole-zero frequencies                                                                 | 61     |

| 4.     | .4.3          | Simulated load-transient response                                                               | 63     |

| 4.5    | Ex            | perimental results                                                                              | 65     |

| 4.     | .5.1          | Open-loop measurement                                                                           | 66     |

| 4.     | .5.2          | SCALDO regulator behaviour against the output capacitor ESR                                     | 69     |

| 4.     | .5.3          | Regulator behaviour against the equivalent resistance of the switching network                  | 72     |

| 4.6    | Co            | mparison of the results                                                                         | 73     |

| 4.     | .6.1          | Frequencies of the open-loop poles and zeros                                                    | 73     |

| 4.     | .6.2          | Effect of the output capacitor ESR on stability                                                 | 74     |

| 4.     | .6.3          | Effect of the resistive parameter of the switching network on sta                               | -      |

| 4.7    | Di            | scussion                                                                                        |        |

| Chapte | er 5 1        | Theoretical Background of the Dual-Output SCALDO Techniqu                                       | e77    |

| 5.1    |               | troduction                                                                                      |        |

| 5.2    |               | ial-polarity SCALDO concept                                                                     |        |

| 5.3    |               | perational modes of the DO-SCALDO technique                                                     |        |

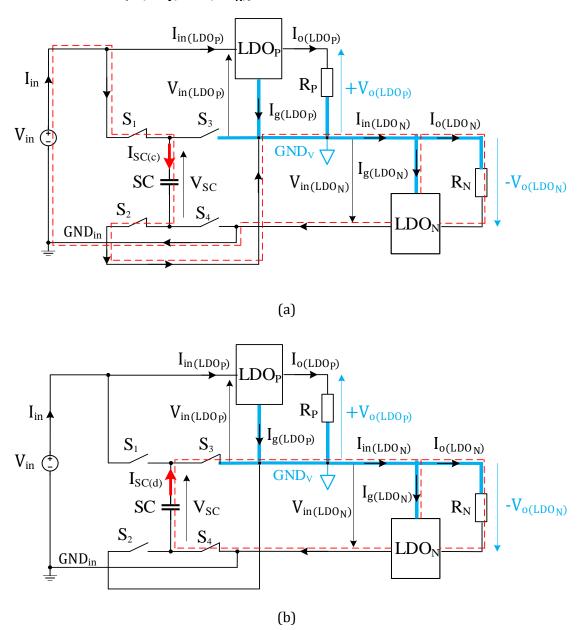

| 5.     | .3.1          | Phase 1: Initial charging process                                                               |        |

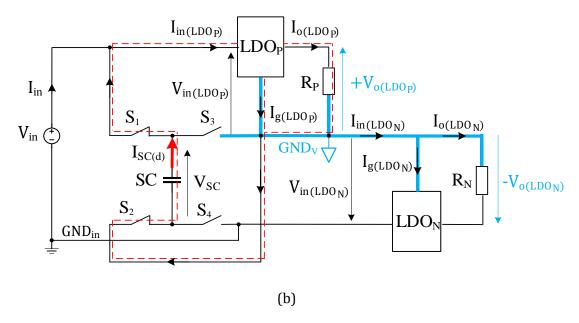

| 5.     | .3.2          | Phase 2: $(I_{O(LDO_P)} > I_{O(LDO_N)})$                                                        |        |

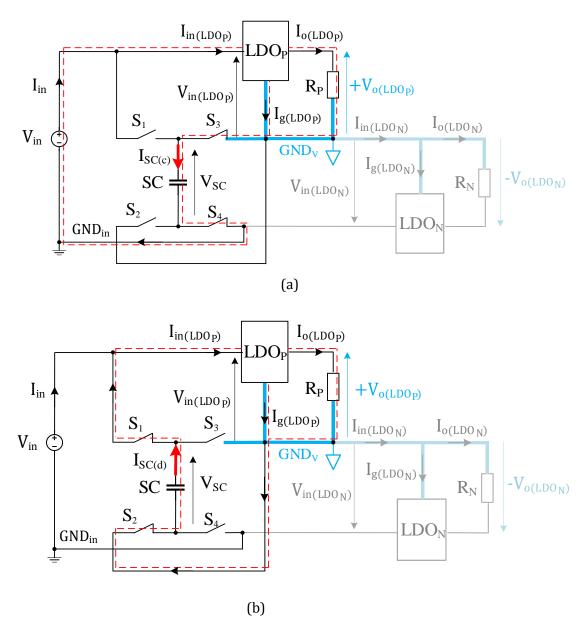

| 5.     | .3.3          | Phase 3: $(I_{O(LDO_P)} < I_{O(LDO_N)})$                                                        |        |

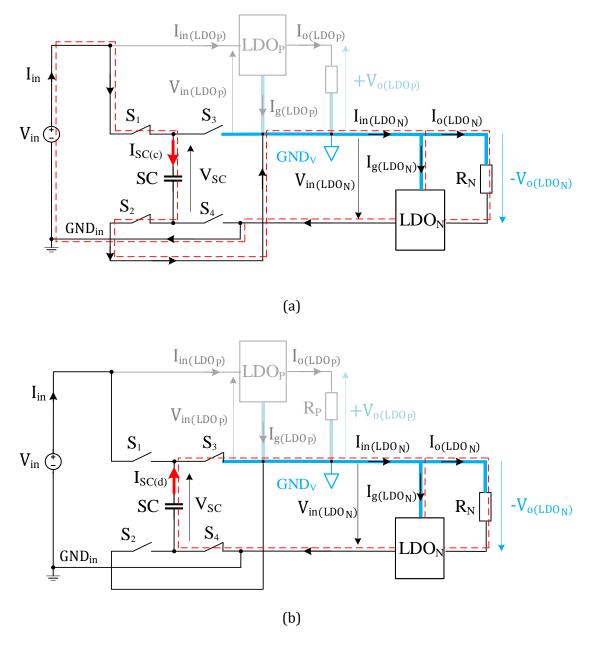

| 5.     | .3.4          | Phase 4: $(I_{o(LDO_P)} = I_{o(LDO_N)})$                                                        |        |

| 5.4    |               | rameters of the circuit modes of the DO-SCALDO regulator                                        |        |

| 5.5    | Pov           | ver losses                                                                  | 89  |

|--------|---------------|-----------------------------------------------------------------------------|-----|

| 5.6    | End           | -to-end efficiency                                                          | 90  |

| 5.7    | Disc          | cussion                                                                     | 91  |

| Chapte | r 6 <b>Ex</b> | xperimental Validation of the DO-SCALDO Concept                             | 92  |

| 6.1    | Imp           | lementation aspects of the 12 V to $\pm 5$ V DO-SCALDO prototype            | 92  |

| 6.2    | Stea          | ndy-state performance                                                       | 95  |

| 6.     | 2.1           | Phase 2 ( $I_{o(LDO_P)} > I_{o(LDO_N)}$ ) observations                      | 95  |

| 6      | 2.2           | Phase 3 ( $I_{o(LDO_P)} < I_{o(LDO_N)}$ ) observations                      | 96  |

| 6.     | 2.3           | Phase 4 ( $I_{o(LDO_P)} = I_{o(LDO_N)}$ ) observations                      | 97  |

| 6      | 2.4           | Operating frequencies                                                       | 97  |

| 6.3    | Loa           | d-transient response                                                        | 98  |

| 6.     | 3.1           | Positive-rail LDO regulator response                                        | 98  |

| 6      | 3.2           | Negative-rail LDO regulator response                                        | 100 |

| 6.4    | Los           | s estimation                                                                | 101 |

| 6.5    | Effi          | ciency estimation                                                           | 102 |

| 6.6    |               | nparison of the basic features of the DO-SCALDO concept with oth            |     |

| 6.5    | -             | t-rail DC-DC converters                                                     |     |

| 6.7    |               | cussion                                                                     |     |

| -      |               | onclusions and Further Research                                             |     |

| 7.1    |               | comes of this research                                                      |     |

|        | 1.1           | Outcomes and conclusions of the stability criterion                         |     |

| 7.     | 1.2           | Outcomes and conclusions of the dual-output SCALDO regulator Implementation |     |

| 7.2    | The           | significance of the findings of this research                               |     |

| 7.3    |               | ommendations for further research                                           |     |

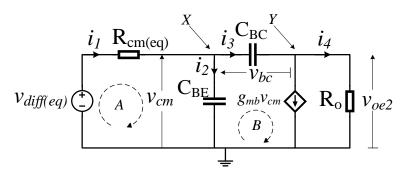

|        |               | Small-Signal Model of the Error Amplifier                                   |     |

|        |               | Schematic and PCB design of the 12 V to 5 V Discrete SCALDO                 |     |

|        |               |                                                                             |     |

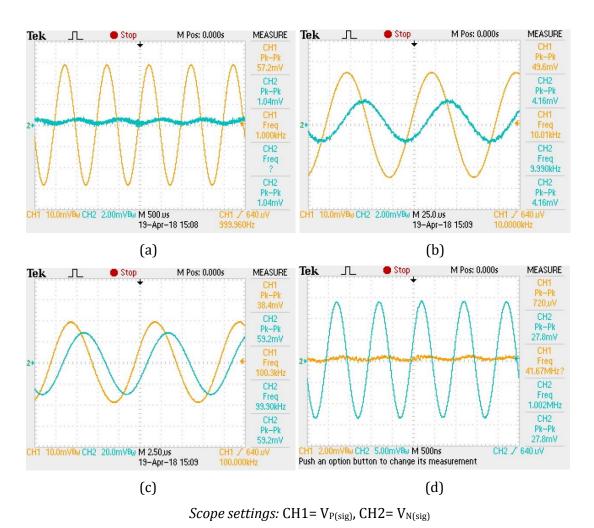

| _      |               | Oscilloscope Traces of the Open-Loop Frequency Measurem                     |     |

|        |               |                                                                             |     |

| Appen  | dix D:        | Schematics and PCB design of the 12 V to ±5 V DO-SCALDO                     |     |

|        |               |                                                                             | 121 |

| Refere | nces          |                                                                             | 125 |

## **List of Figures**

| Figure 1-1: Development stages of the SCALDO technique                           | 3      |

|----------------------------------------------------------------------------------|--------|

| Figure 1-2: The fundamental circuit configuration of the SCALDO technique:       | (a) S0 |

| charging phase (b) SC discharging phase                                          | 3      |

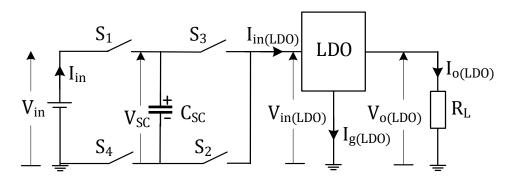

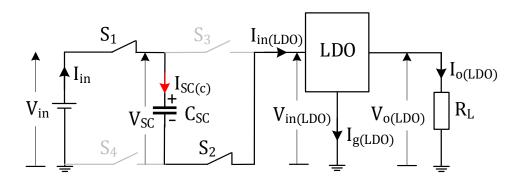

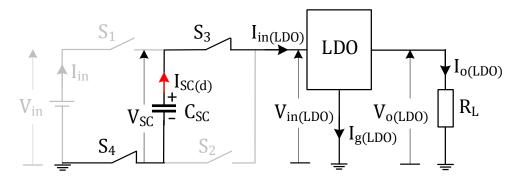

| Figure 2-1: The configuration of the fundamental SCALDO regulator.               | 8      |

| Figure 2-2: The charging phase of the fundamental SCALDO regulator               | 8      |

| Figure 2-3: The discharging phase of the fundamental SCALDO regulator            | 9      |

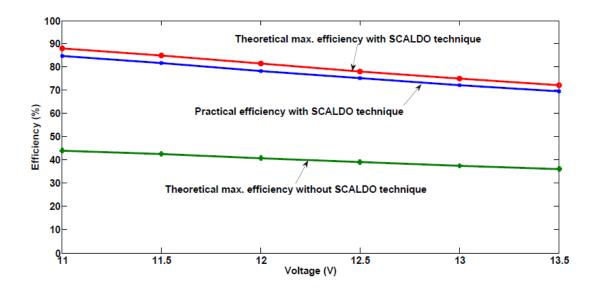

| Figure 2-4: The end-to-end efficiency advantage of a 12 V to 5 V SCALDO reg      | ulator |

|                                                                                  | 10     |

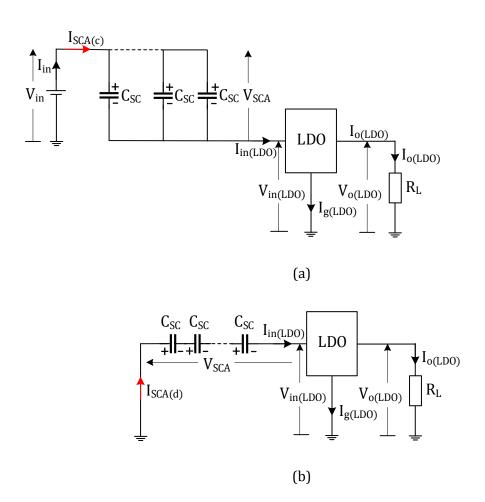

| Figure 2-5: Series to Parallel SC Array SCALDO configuration: (a) SC charging    | phase  |

| (b) SC discharging phase.                                                        | 12     |

| Figure 2-6: Parallel to Series SC Array SCALDO configuration: (a) SC charging    | phase  |

| (b) SC discharging phase.                                                        | 13     |

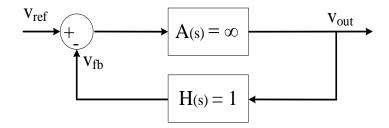

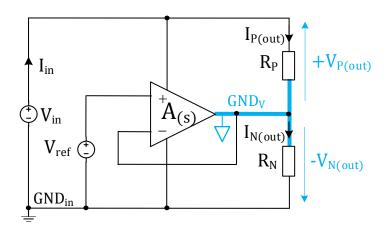

| Figure 2-7: The voltage control loop of a buffer circuit                         | 18     |

| Figure 2-8: A basic schematic of a unity-gain buffer circuit.                    | 18     |

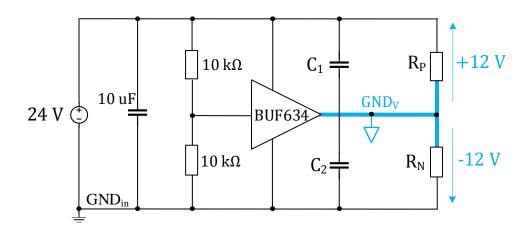

| Figure 2-9: A ±12 V split-rail converter with BUF 634 IC                         | 19     |

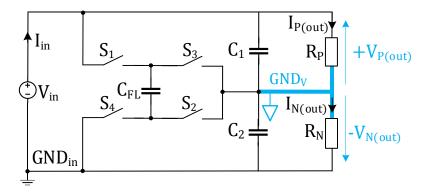

| Figure 2-10: The basic configuration of a switched-capacitor split-rail circuit. | 20     |

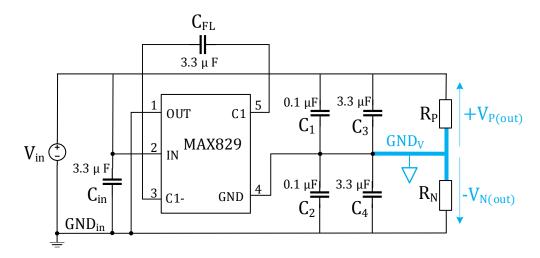

| Figure 2-11: Use of MAX829 as a charge pump split-rail converter                 | 21     |

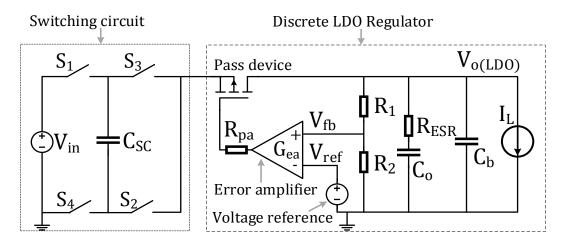

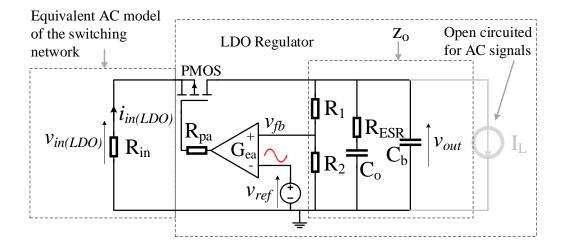

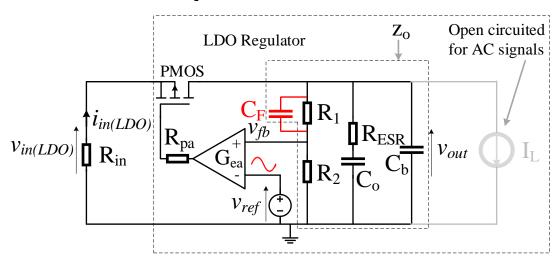

| Figure 3-1: The basic circuit diagram of the discrete SCALDO regulator           | 25     |

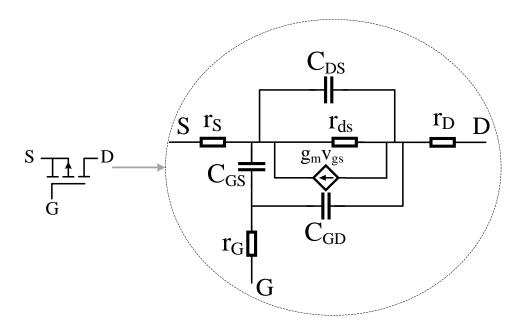

| Figure 3-2: The small-signal model of the PMOS transistor.                       | 26     |

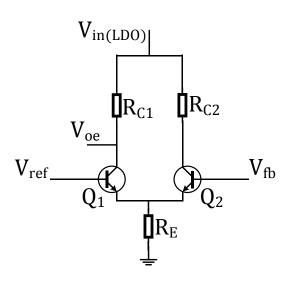

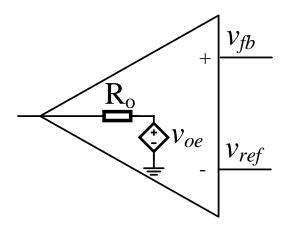

| Figure 3-3: The NPN BJT differential pair.                                       | 27     |

| Figure 3-4: The simplified error amplifier model                                 | 28     |

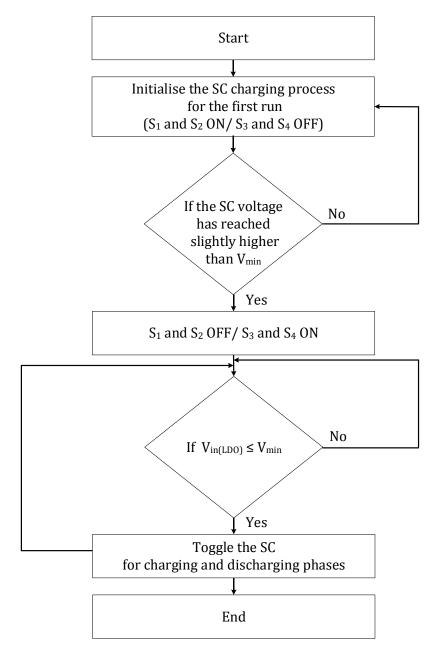

| Figure 3-5: The switching algorithm of the basic SCALDO topology                 | 29     |

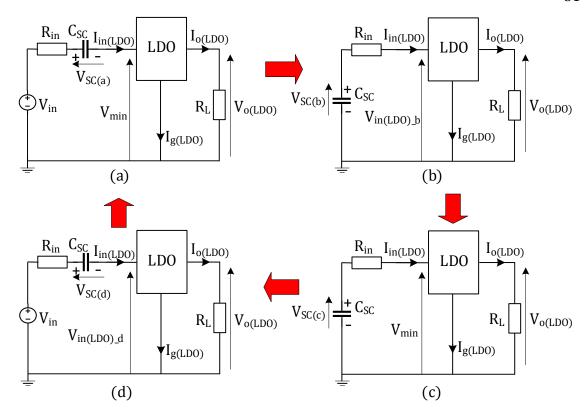

| Figure 3-6: SCALDO operation cycle: (a) End of the charging phase, (b) Start     | of the |

| discharging phase, (c) End of the discharging phase, (d) Start of the charging   | phase  |

|                                                                                  | 31     |

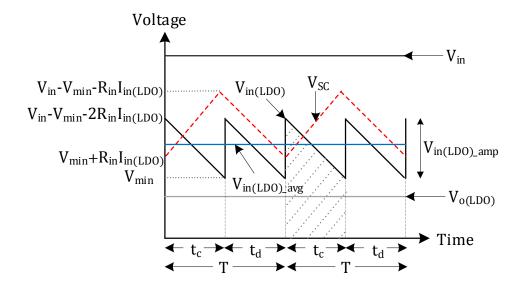

| Figure 3-7: The variation of voltages of the single-stage SCALDO regulator       | 32     |

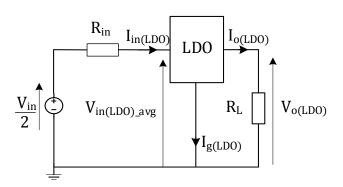

| Figure 3-8: The equivalent circuit model of the SCALDO regulator.                | 32     |

| Figure 3-9: The linear circuit model of the SCALDO regulator                     | 33     |

| Figure 3-10: The small-signal model of the SCALDO regulator                      | 34     |

| Figure 3-11: The voltage control loop of the basic SCALDO topology               | 37     |

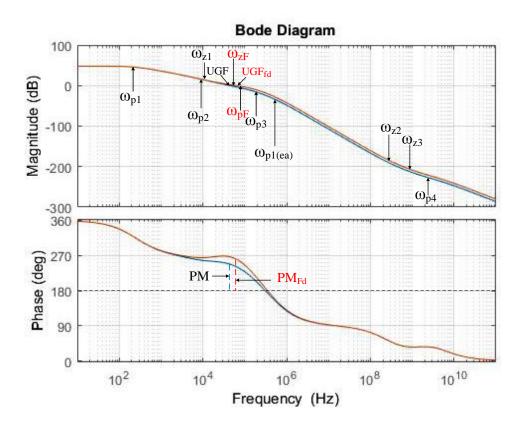

| Figure 3-12: Bode plot of the SCALDO regulator.                                  | 39     |

| Figure 3-13: Feedforward compensation of the SCALDO regulator                    | 42     |

| Figure 3-14: Bode plot of the SCALDO regulator when the feedforward                                                              |

|----------------------------------------------------------------------------------------------------------------------------------|

| compensation is used along with the output capacitor ESR compensation43                                                          |

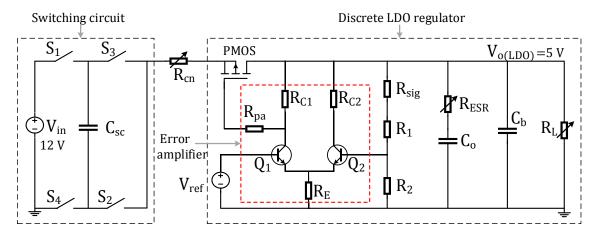

| Figure 4-1: The experimental design of the discrete SCALDO regulator47                                                           |

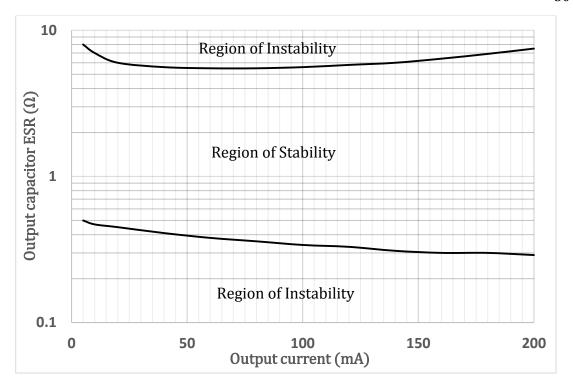

| Figure 4-2: The stable range of the output capacitor ESR of the SCALDO regulator                                                 |

| 50                                                                                                                               |

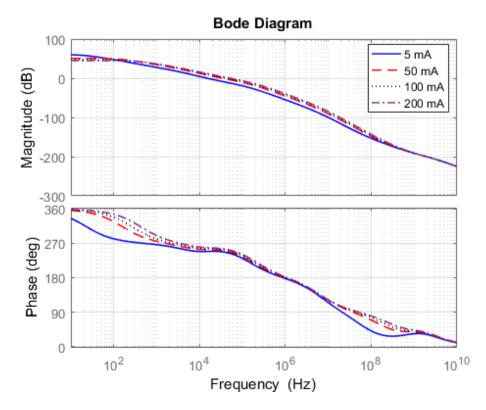

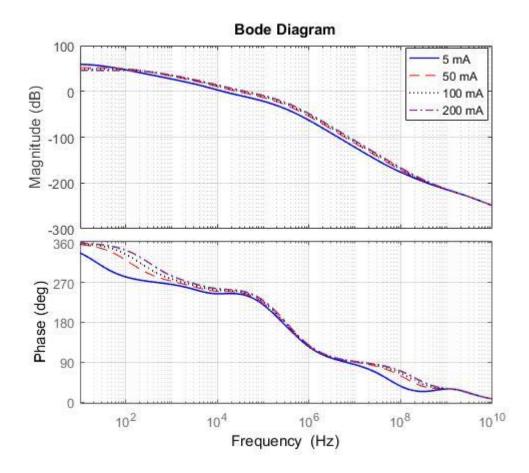

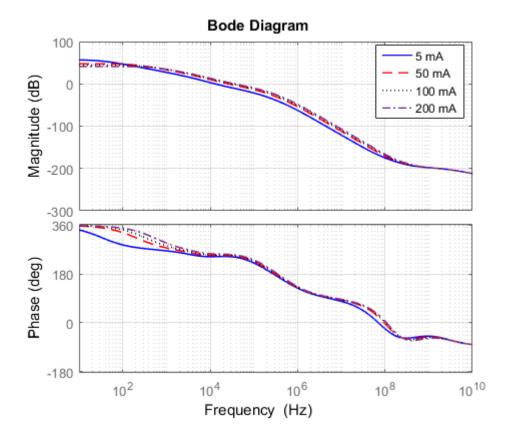

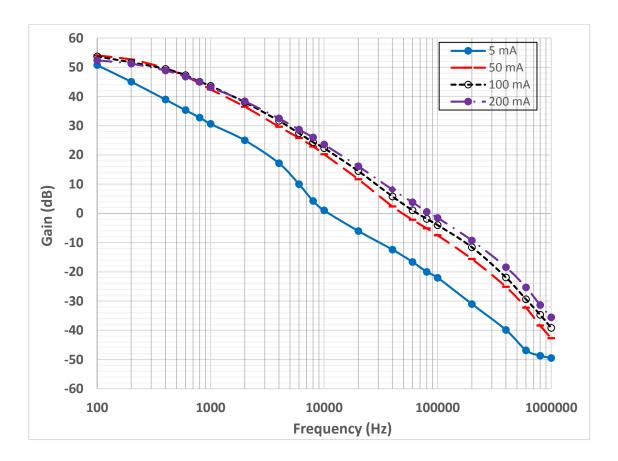

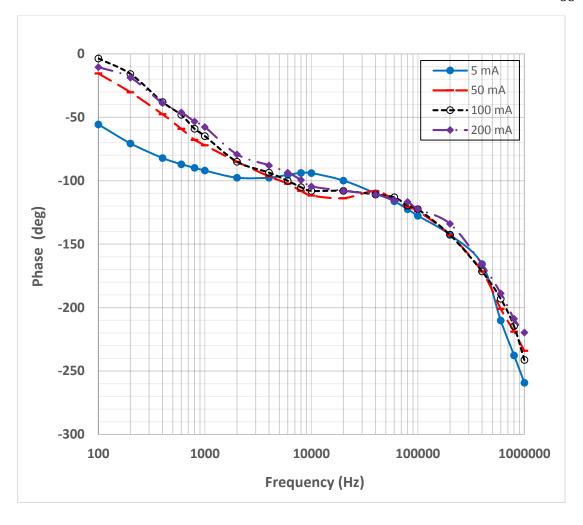

| Figure 4-3: Calculated phase and gain behaviour of the SCALDO regulator for                                                      |

| different levels of load current50                                                                                               |

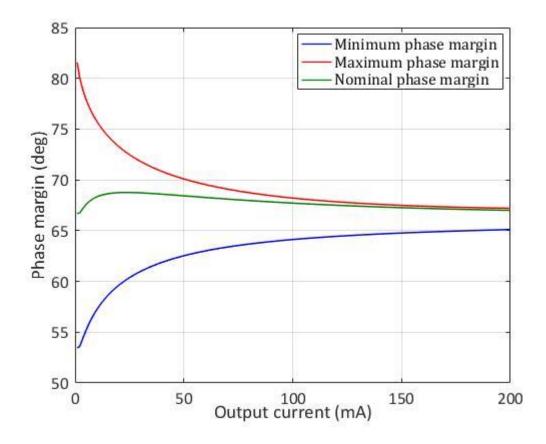

| Figure 4-4: Extreme variation of the phase margin against the load current54                                                     |

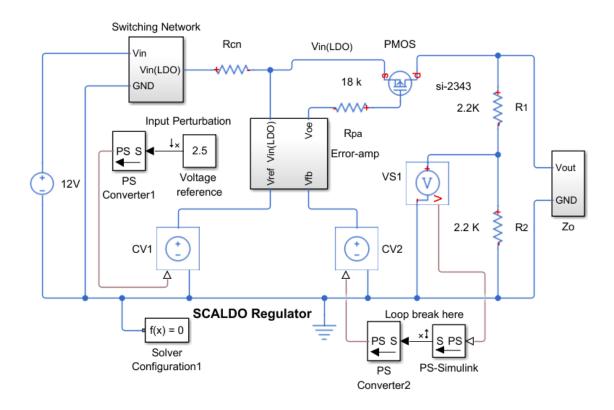

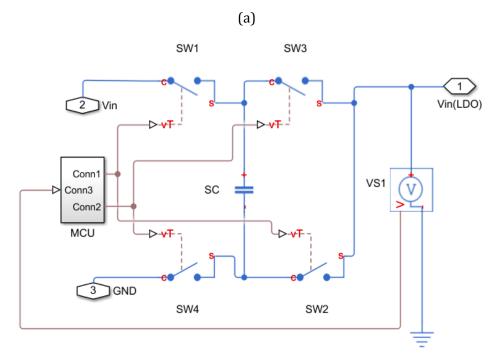

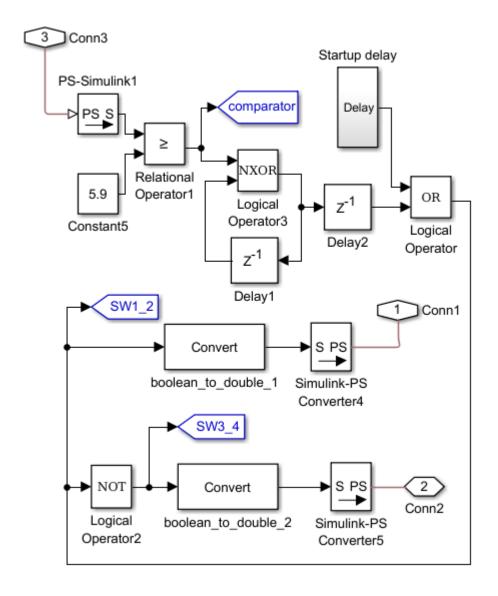

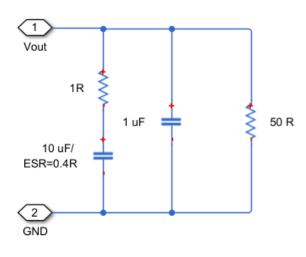

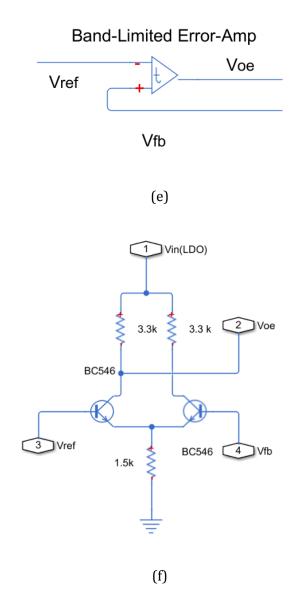

| Figure 4-5: The simulation model of the SCALDO Regulator: (a) Compacted model                                                    |

| (b) Switching Network, (c) Logic circuit (MCU) (d) Output impedance ( $z_0$ ), (e) first-                                        |

| order model of the error amplifier, (f) high-frequency model of the error amplifier                                              |

| 58                                                                                                                               |

| Figure 4-6: Simulated phase and gain behaviour of the SCALDO regulator for the                                                   |

| first-order model of the error amplifier60                                                                                       |

| Figure 4-7: Simulated phase and gain behaviour of the SCALDO regulator for the                                                   |

| high-frequency model of the error amplifier61                                                                                    |

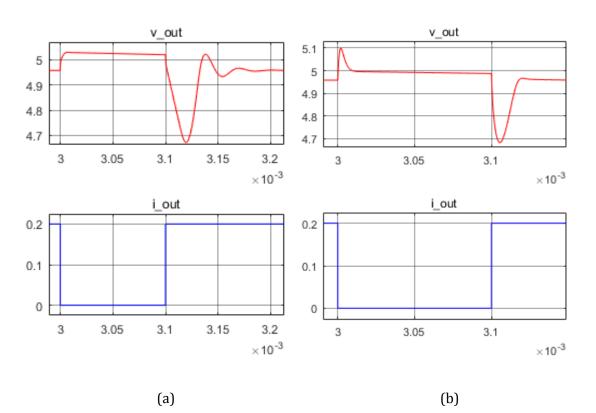

| Figure 4-8: Simulated load-transient response for different ESR values of the output                                             |

| capacitor: (a) $R_{ESR} = 0.4 \Omega$ , (b) $R_{ESR} = 1.4 \Omega$ , (c) $R_{ESR} = 5.4 \Omega$ , (d) $R_{ESR} = 10.4 \Omega$ 64 |

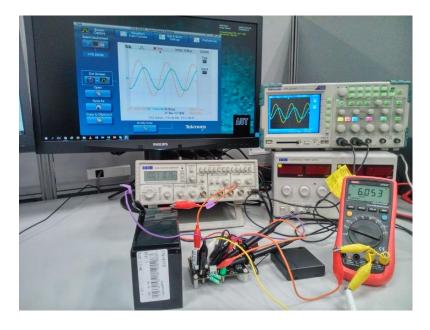

| Figure 4-9: The experimental setup of the stability analysis65                                                                   |

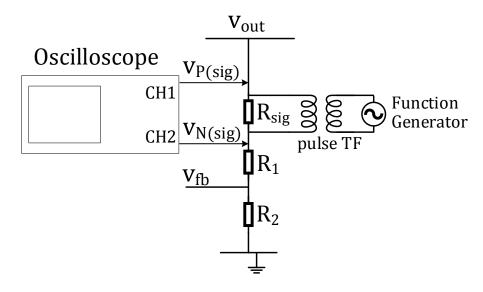

| Figure 4-10: The signal injecting method66                                                                                       |

| Figure 4-11: Experimental frequency response of the SCALDO regulator: (a) Open-                                                  |

| loop gain, (b) Open-loop phase68                                                                                                 |

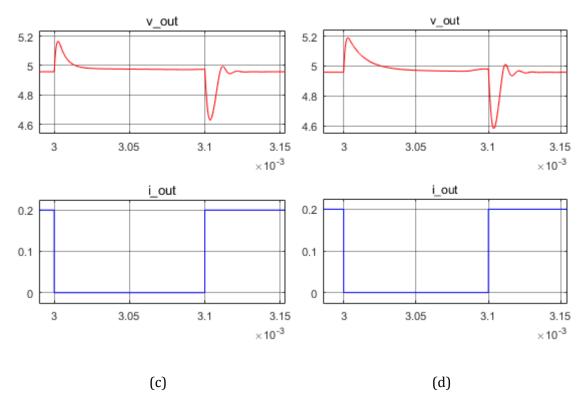

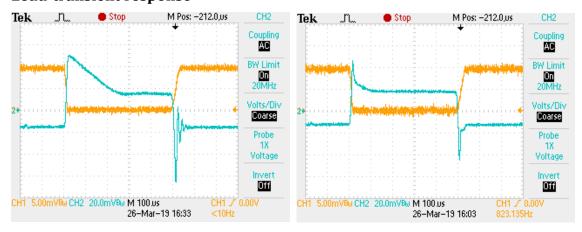

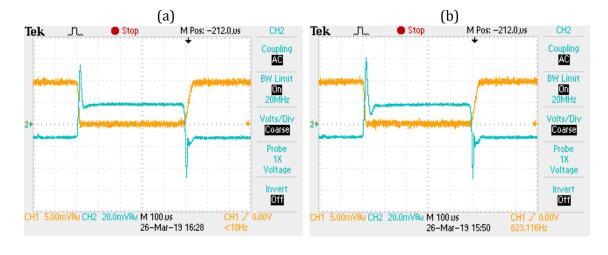

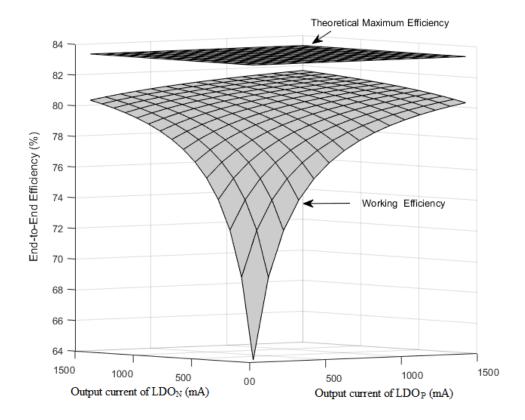

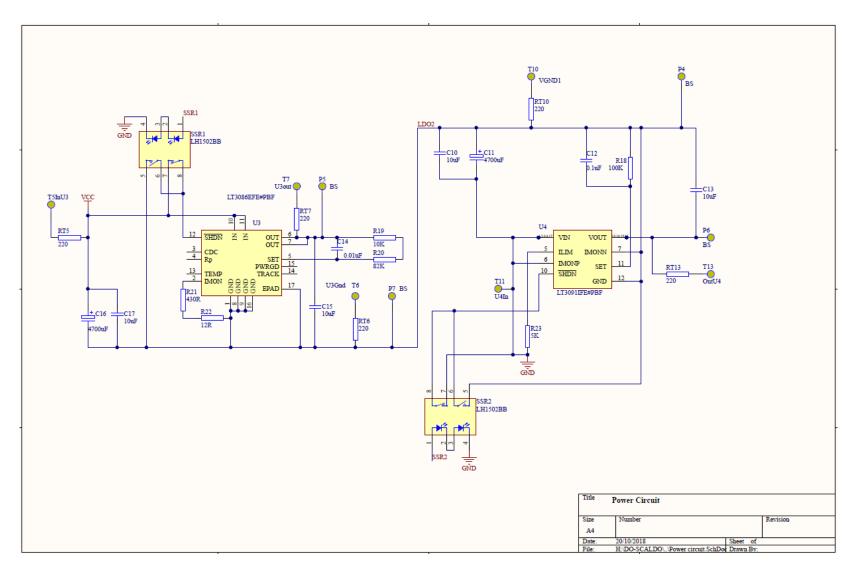

| Figure 4-12: Experimental load-transient response for different ESR values of the                                                |

| output capacitor: (a) $R_{ESR}=0.4~\Omega$ , (b) $R_{ESR}=1.4~\Omega$ , (c) $R_{ESR}=5.4~\Omega$ , (d) $R_{ESR}=10.4~\Omega$     |

| 70                                                                                                                               |

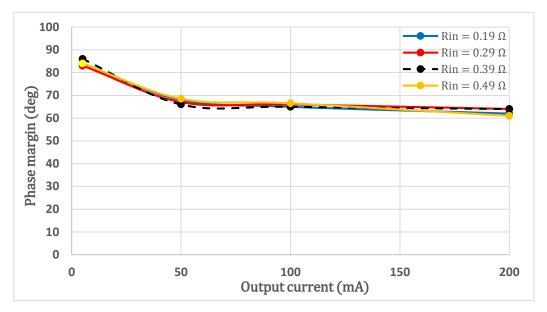

| Figure 4-13: The experimental phase margin variation against the equivalent                                                      |

| resistance of the switching network72                                                                                            |

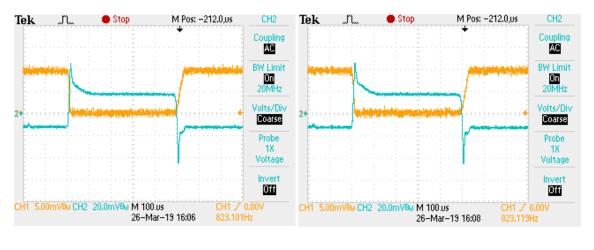

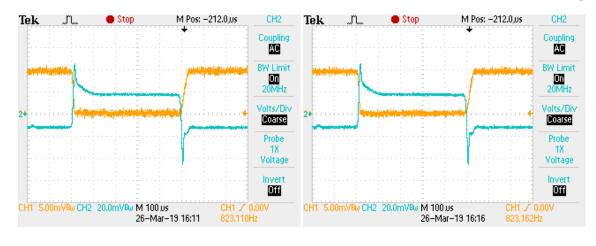

| Figure 4-14: Load-transient response over equivalent resistance of the switching                                                 |

| network: (a) $R_{in} = 0.19 \Omega$ , (b) $R_{in} = 0.29 \Omega$ , (c) $R_{in} = 0.39 \Omega$ , (d) $R_{in} = 0.49 \Omega$ 73    |

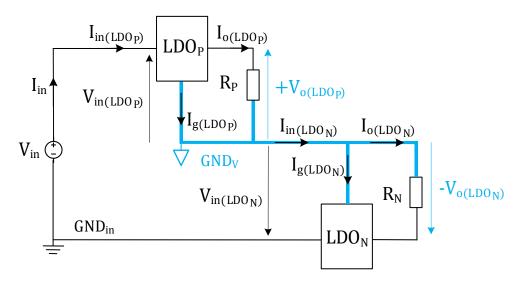

| Figure 5-1: Cascaded positive and negative LDO regulators with dual-polarity                                                     |

| outputs78                                                                                                                        |

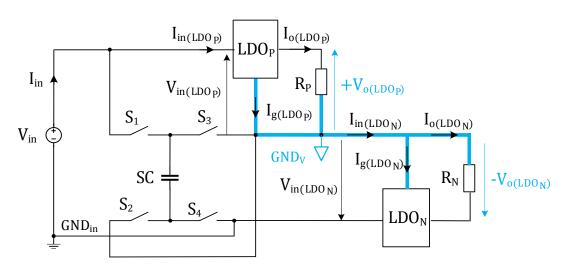

| Figure 5-2: The cascaded dual LDO regulators with the SCALDO approach79                                                          |

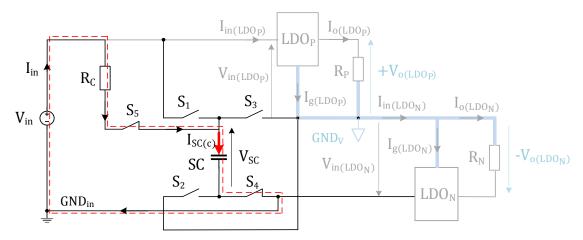

| Figure 5-3: Initial charging process                                                                                             |

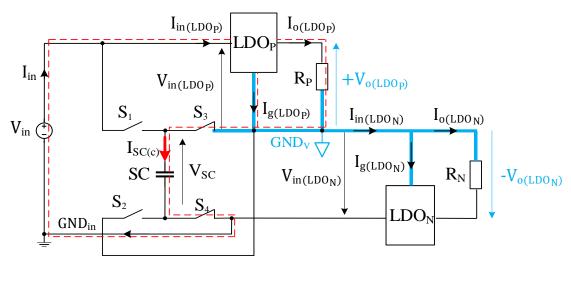

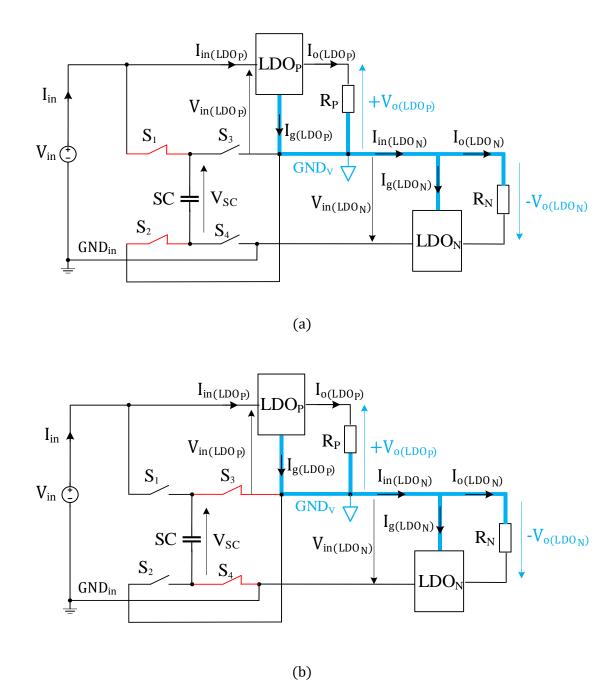

| Figure 5-4: DO-SCALDO circuit operation in phase 2: (a) charging cycle (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| discharging cycle82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 5-5: Basic SCALDO operation when the LDO $_{N}$ is OFF: (a) charging cycle (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| discharging cycle83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 5-6: DO-SCALDO circuit operation in phase 3: (a) charging cycle (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| discharging cycle84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 5-7: Basic SCALDO operation when the $LDO_P$ is inactive; (a): SC charging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| phase (b): SC discharging phase85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 5-8: DO-SCALDO circuit operation in phase 4 (a) SC is in parallel to the LDO $_{\rm F}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (b) SC is in parallel to the $LDO_N$ 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

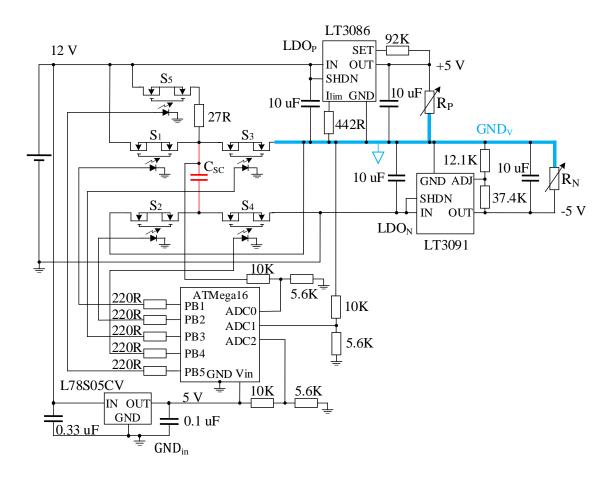

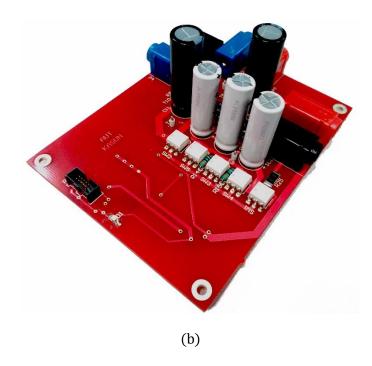

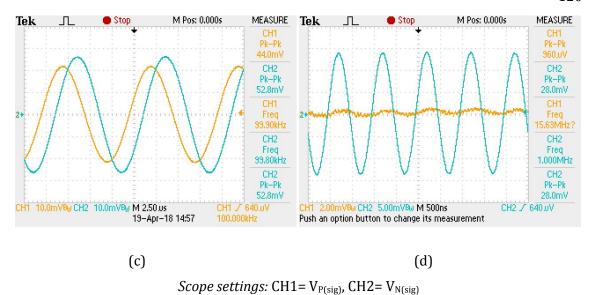

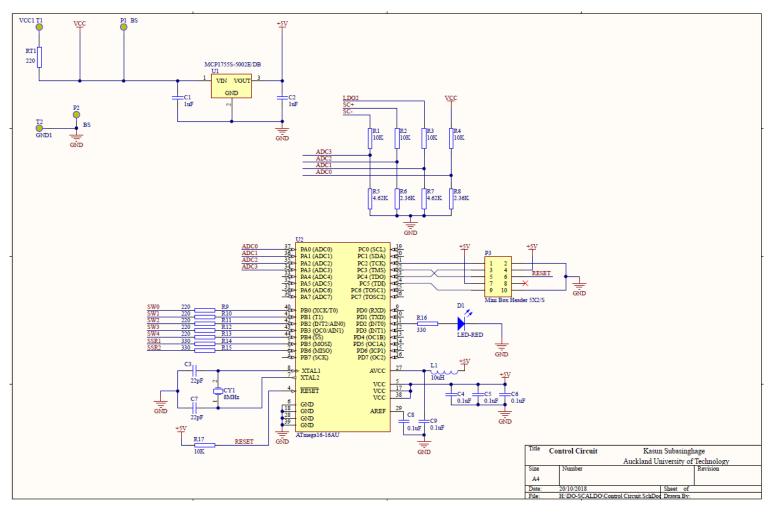

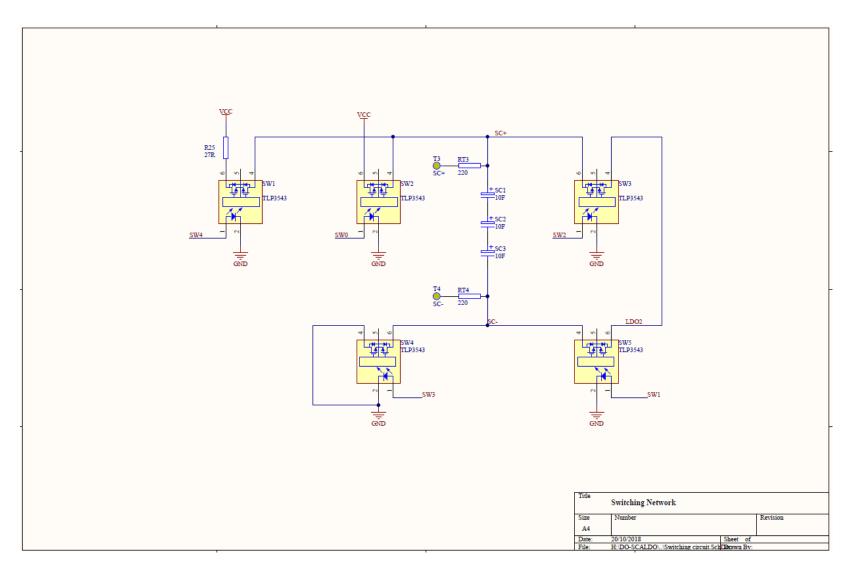

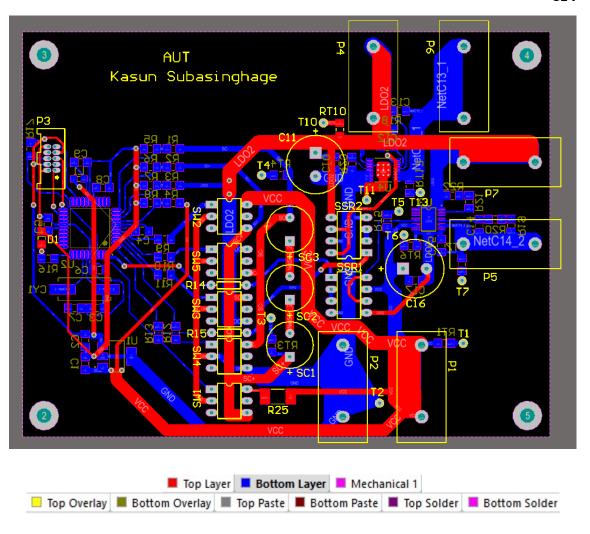

| Figure 6-1: The 12 V to $\pm 5$ V DO-SCALDO proof of concept prototype: (a) schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (b) PCB design93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

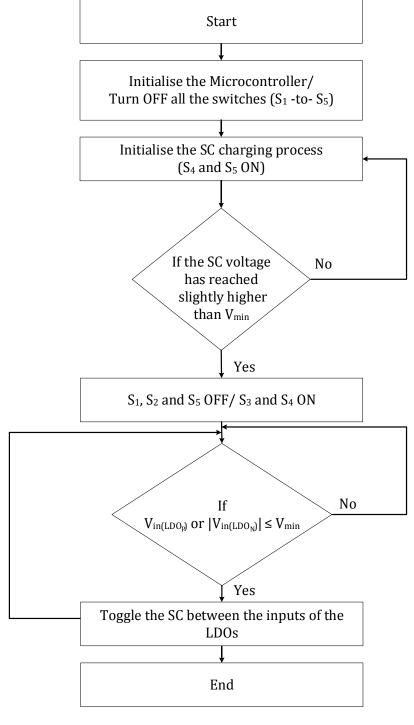

| Figure 6-2: The MCU algorithm of the prototype94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

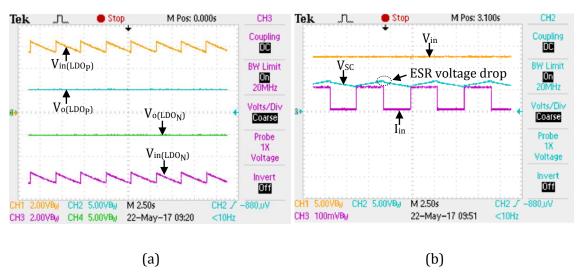

| Figure 6-3: Steady-state results of phase 2 when $I_{o(LDO_P)}$ = 1100 mA and $I_{o(LDO_N)}$ = 100 mA and $I_{o(LDO_N)}$ |

| mA; (a): Input and output voltages of the LDOs (b): Voltage and current of the power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| source, voltage across the supercapacitor95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 6-4: Steady-state results of phase 3 when $I_{o(LDO_P)}$ = 100 mA and $I_{o(LDO_N)}$ = 1100 mA and $I_{o(LDO_N)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| mA; (a): Input and output voltages of the LDOs (b): Voltage and current of the power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| source, voltage across the supercapacitor96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

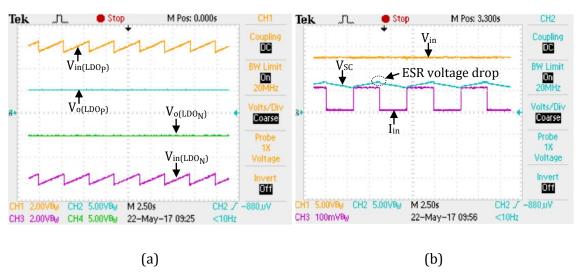

| Figure 6-5: Steady-state results of phase 4 when $I_{o(LDO_P)}$ = 1000 mA and $I_{o(LDO_N)}$ =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1000 mA; (a): Input and output voltages of the LDOs (b): Voltage and current of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| power source, voltage across the supercapacitor97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

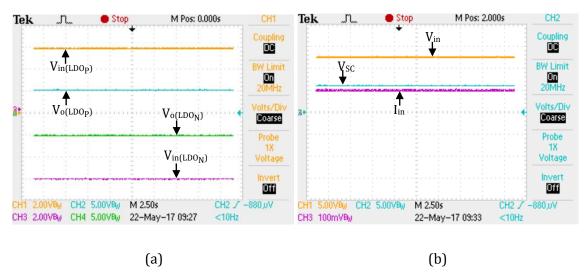

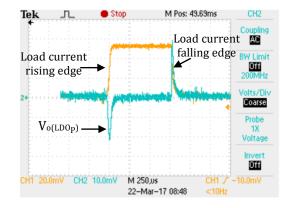

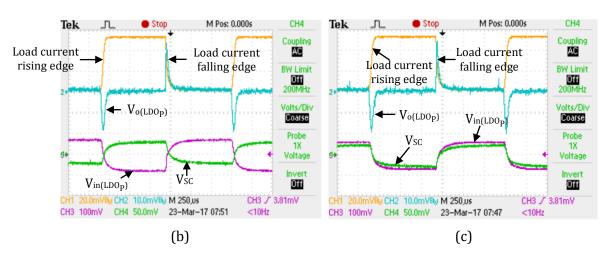

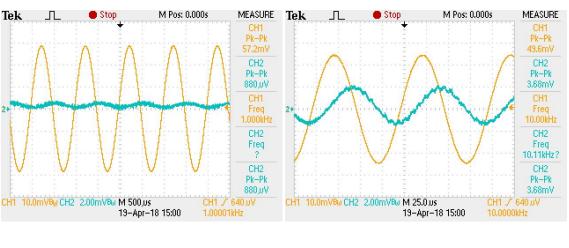

| Figure 6-6: Load-transient measurement of LDO <sub>P</sub> ; (a): Before applying the SCALDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| method (b): After applying the SCALDO method - SC charging phase (c) SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| discharging phase99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

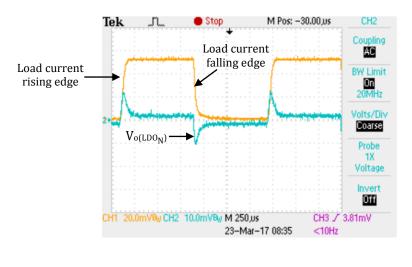

| Figure 6-7: Load-transient measurement of LDO <sub>N</sub> ; (a): Before applying the SCALDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| technique (b): After applying the SCALDO technique - SC charging phase (c) SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| discharging phase101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

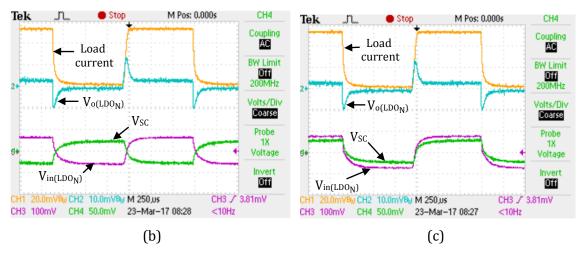

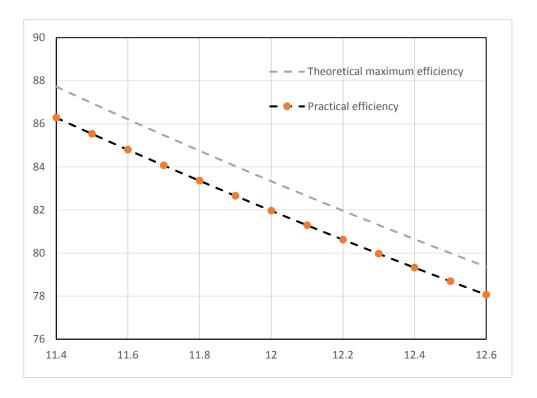

| Figure 6-8: End-to-end efficiency of the 12 V to $\pm$ 5 V split-rail regulator at the rated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| input voltage102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 6-9: End-to-end efficiency for ± 5% difference of the rated input voltage at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| maximum load current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |